# Illia Ostapyshyn

# Enhancing Energy Efficiency with Advanced DRAM Management in Linux

Master's Thesis November 1, 2024

# **Enhancing Energy Efficiency with Advanced DRAM Management in Linux**

Masterarbeit im Fach Technische Informatik

vorgelegt von

Illia Ostapyshyn

angefertigt am

Institut für Systems Engineering Fachgebiet System- und Rechnerarchitektur

Fakultät für Elektrotechnik und Informatik Leibniz Universität Hannover

Erstprüfer: **Prof. Dr.-Ing. habil. Daniel Lohmann**Zweitprüfer: **Prof. Dr.-Ing. Christian Dietrich**Betreuer: **Alexander Halbuer, M.Sc.**

Beginn der Arbeit: **19. April 2024**Abgabe der Arbeit: **1. November 2024**

# Erklärung

Ich versichere, dass ich die Arbeit ohne fremde Hilfe und ohne Benutzung anderer als der angegebenen Quellen angefertigt habe und dass die Arbeit in gleicher oder ähnlicher Form noch keiner anderen Prüfungsbehörde vorgelegen hat und von dieser als Teil einer Prüfungsleistung angenommen wurde. Alle Ausführungen, die wörtlich oder sinngemäß übernommen wurden, sind als solche gekennzeichnet.

### Declaration

I declare that the work is entirely my own and was produced with no assistance from third parties. I certify that the work has not been submitted in the same or any similar form for assessment to any other examining body and all references, direct and indirect, are indicated as such and have been cited accordingly.

(Illia Ostapyshyn) Hannover, 1. November 2024

### **ABSTRACT**

In contrast to the early days of computing, memory is no longer a scarce resource. The capacity of dynamic random-access memory (DRAM) continues to successfully scale with ever-growing requirements of the applications. Modern server systems can house terabytes of DRAM, yet in the large-scale data centers, the average memory utilization does not exceed 70 percent. Especially in such systems, memory is a major contributor to the overall power consumption, prompting the question of whether it is possible to deactivate unused memory to conserve energy. However, neither hardware nor software offer sufficient support to realize these energy savings and millions of systems continue to expend energy on maintaining unused memory.

On the hardware side, the existing power-saving modes are only applicable at the large granularities of ranks and channels (>8 GiB). This is slowly changing with the LPDDR5 standard introducing the PARC feature and bringing the power management granularity to the sub-rank level of around 1 GiB. On the software side, contemporary operating systems are still designed around the notion of memory scarcity. They primarily manage memory in 4 KiB pages and operate under the assumption that unused memory is a wasted resource. Over time, the available memory is filled with file cache and used memory inevitably becomes scattered across all memory devices. Consequently, it becomes impossible to find unused contiguous segments of memory for deactivation in any modern system with considerable uptime. In a nutshell, the possibility of memory power management contradicts the foundational assumptions of the conventional memory management.

This work approaches the lack of power-saving mechanisms from the systems software perspective. It demonstrates that also Linux suffers from poor memory management, as the memory quickly becomes unsuitable for deactivation and remains in this state even if the utilization declines. To tackle this issue, the thesis proposes a novel compaction mechanism designed with DRAM power management in mind. Applied to real-world workloads, it successfully increases the amount of unused memory segments and reduces the power consumption of a desktop system under heavy load by up to 19.1 mW. These savings scale quickly when applied to numerous systems with overprovisioned memory worldwide. Ultimately, this work is the first to reveal that it actually pays off to actively reorganize memory contents with the goal of energy savings: the energy invested in a single compaction procedure is recovered in just under one minute.

# KURZFASSUNG

Im Gegensatz zu den frühen Tagen der Rechnertechnik ist Speicher heute keine knappe Ressource mehr. Dynamic Random Access Memory (DRAM) skaliert erfolgreich mit den ständig wachsenden Anforderungen der Anwendungen. Heutige Serversysteme können Terabytes an DRAM enthalten, doch in den großen Rechenzentren liegt die durchschnittliche Speicherauslastung unter 70 Prozent. Gerade in solchen Systemen trägt der Speicher wesentlich zum gesamten Stromverbrauch bei. Dies wirft die Frage auf, ob es möglich ist, ungenutzten Speicher zu deaktivieren, um Energie zu sparen. Allerdings bieten weder Hardware noch Software ausreichende Unterstützung, um diese Energieeinsparungen zu realisieren. Somit verschwenden Millionen von Systemen weiterhin Energie für ungenutzten Speicher.

Auf der Hardwareseite sind die vorhandenen Stromsparmechanismen nur auf die große Granularität der Ranks und Kanäle (>8 GiB) anwendbar. Dies ändert sich mit dem LPDDR5-Standard, der die PARC-Funktion einführt und die Granularität der Energieverwaltung auf die Sub-Rank-Ebene von etwa 1 GiB reduziert. Auf der Softwareseite sind die heutigen Betriebssysteme immer noch auf Speicherknappheit ausgelegt. Sie verwalten den Speicher hauptsächlich in 4-KiB-Seiten und betrachten ungenutzten Speicher als eine verschwendete Ressource. Im Laufe der Zeit wird der verfügbare Speicher mit dem Datei-Cache gefüllt und der verwendete Speicher wird unvermeidlich über alle Speicherbausteine verstreut. Folglich wird es in einem modernen System mit langer Betriebszeit unmöglich, komplett ungenutzte Speichersegmente zu finden, um sie zu deaktivieren. Schlussendlich steht die Möglichkeit der Speicher-Energieverwaltung im Widerspruch zu den grundlegenden Annahmen der konventionellen Speicherverwaltung.

In dieser Arbeit werden fehlende Stromsparmechanismen aus der Perspektive der Systemsoftware betrachtet. Sie zeigt, dass die Speicherverwaltung auch in Linux suboptimal ist. Der Speicher nimmt schnell einen Zustand an, wo jegliche Deaktivierung verhindert wird, und behält ihn bei, selbst wenn die Auslastung sinkt. Um das Problem zu lösen wird in dieser Arbeit ein neuartiger Mechanismus zur Speicherkompaktifizierung speziell für DRAM-Energieverwaltung entwickelt. Angewandt auf reale Arbeitslasten erhöht er erfolgreich die Menge der ungenutzten Speichersegmente und reduziert den Stromverbrauch eines Desktop-Systems unter schwerer Last um bis zu 19,1 mW. Diese Einsparungen skalieren schnell, wenn der Mechanismus auf eine Vielzahl von Systemen mit überprovisioniertem Speicher weltweit angewendet wird. Diese Arbeit zeigt zum ersten Mal, dass es sich lohnt, Speicherinhalt zur Energieeinsparung aktiv zu reorganisieren. Die in einem einzigen Kompaktifizierungsvorgang investierte Energie wird in weniger als einer Minute zurückgewonnen.

# **CONTENTS**

| Abstract                                                                                                                                                                                                                                                                    | V   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Kurzfassung                                                                                                                                                                                                                                                                 | vii |

| Contents                                                                                                                                                                                                                                                                    | ix  |

| 1 Introduction                                                                                                                                                                                                                                                              | 1   |

| 2 Fundamentals 2.1 Dynamic Random-Access Memory 2.1.1 Standardization 2.1.2 Information Storage 2.1.3 Hierarchy 2.1.4 Refresh Mechanisms 2.1.5 Power-Saving Modes 2.2 Operating Systems 2.2.1 Page-Frame Allocator 2.2.2 Disk Caching 2.2.3 Page Migration 2.3 Related Work |     |

| 3 Architecture 3.1 Concept 3.1.1 Understanding Fragmentation 3.1.2 Optimal Compaction 3.2 Implementation 3.2.1 Data Structures 3.2.2 Slice Isolation 3.2.3 Migration Target Search 3.2.4 Slice Onlining 3.2.5 Price Model 3.2.6 User Interface 3.3 Discussion               |     |

| 4 Analysis  4.1 Setup and Methodology                                                                                                                                                                                                                                       |     |

#### Contents

| 4.3 Case Studies                    | 41       |

|-------------------------------------|----------|

| 4.3.1 LLVM Compilation              | 43       |

| 4.3.2 TPC-H Queries                 | 45       |

| 4.3.3 OpenStreetMap Import          | 47       |

| 4.3.4 Discussion                    | 48       |

| 4.4 Effect on Latency               | 50       |

| 4.4.1 Discussion                    | 51       |

| <b>5 Conclusion</b> 5.1 Future Work | 53<br>54 |

| List of Acronyms                    | X        |

| List of Figures                     | xii      |

| List of Tables                      | XV       |

| List of Algorithms                  | xvi      |

| References                          | xix      |

INTRODUCTION

In the early days of computing, memory was a scarce resource. The main memory was typically implemented as a magnetic-core memory with magnetic ring cores threaded onto wires that can be read or written by applying current [1]. Although the magnetic-core memory provided adequate speeds for the processors of that time, it was costly to produce, limiting its maximum capacity. This limitation led to the introduction of two-tiered storage systems, which divided the memory into fast, low-capacity *primary* core storage and a slow, higher-capacity *secondary* drum storage. The secondary storage enabled execution of programs with working sets larger than what the primary storage could offer. However, this new capability came at the cost of significantly complicating algorithms. Accessing secondary storage required special routines and the logic to load data from the secondary into the primary storage had to be incorporated directly into the algorithms.

This changed with introduction of *virtual memory* [2, 3]. The idea of the virtual memory is to abstract the complete storage resources of the system in a single address space. The secondary storage can be mapped into this address space and accessed by programs as if it were primary storage, without complicating their logic. This abstraction is supported by the operating system, which now transparently implements the exchanging routines. It loads data from the secondary into the primary storage on demand and evicts it when the primary storage becomes full.

Inadvertently, virtual memory—specifically its first [3] and most common implementation, *paging*—solved¹ another problem: *external fragmentation*. External fragmentation occurs when memory is allocated in chunks of different sizes. Over time, as these chunks are allocated and freed, a once large and contiguous area of free memory inevitably becomes divided into smaller, noncontiguous pieces. Eventually, an allocation request might fail as there is no contiguous free chunk of the required size in the memory, even though the total free memory—if combined—would be sufficient to fulfill the request.

The technique of paging solves the problem of external fragmentation by defining a base unit of memory management, the *page*. A page is typically 4 KiB in size. The virtual memory provides a translation mechanism, which allows every page in the virtual address space to be mapped to a contiguous *page frame* in the *physical address space*. As a consequence, the exact locations of the page frames in the *physical memory become irrelevant*. Even if scattered arbitrarily throughout the memory *physically*, the translation mechanism is able to present them as a contiguous region *virtually*. This greatly simplifies the memory management of the system.

The elegance of paging has led to the 4 KiB page becoming a standard for sharing memory between the OS, applications, and even external devices. Without the need to manage memory chunks of different sizes, the OS memory management has evolved with two assumptions: "all page frames are equal" and "only used memory is good memory." With no concern for fragmentation, the OS lacks initiative to keep memory unallocated and trades it for performance by filling it with the cache of the secondary storage (also known as page cache). The page cache remains in memory until the memory shortage occurs, at which point it can be easily evicted.

<sup>&</sup>lt;sup>1</sup>Or rather transformed it into the problem of internal fragmentation, which is not as severe.

#### The return of external fragmentation

The first challenge to these assumptions came as soon as the early 1990s, when the original Pentium processor introduced the Page Size Extension (PSE) feature. PSE extended the virtual memory with support of larger 4 MiB pages that can coexist with the regular 4 KiB pages [4]. This feature persisted, and modern systems now support 2 MiB *huge* and 1 GiB *giant* page frames. The usage of these larger page frames puts less pressure on the translation mechanism and can potentially improve application performance. However, their introduction brings back the problem of external fragmentation, giving the OS a new reason to have free contiguous blocks of size larger than 4 KiB at its disposal. Consequently, there is a substantial body of research analyzing benefits of huge pages and proposing mechanisms for their management [5–11].

By the end of 1970s, the magnetic core memories were phased out in favor of their more efficient semiconductor counterparts [12]. The primary memory today is implemented as *dynamic random-access memory (DRAM)*, which has excelled in scaling its density to meet the ever-increasing demands of applications. This memory is not a scare resource anymore: the price per gigabyte approaches the value of \$1 [13]. Meanwhile, modern server CPUs support up to 24 DRAM modules and such modules can reach 256 GiB in size, yielding 6 TiB of memory in total [14]. These factors make it economically feasible to equip the system with extra capacity, in case it is occasionally required for a demanding task.

Nevertheless, the substantial amounts of DRAM in use come with significant running costs. As each new generation doubles the device capacity, the energy consumption rises correspondingly [15]. Many studies attribute over 30 percent of the total energy consumption in data centers to DRAM [16–18], and this figure is expected to steadily increase. Meanwhile, the average memory utilization remains as low as 40 – 70 percent [19–21]. To handle usage spikes, memory in these systems is often overprovisioned, leading to excessive capacity that goes unused most of the time. A significant share of DRAM's power consumption is independent of its usage: up to 20 percent are required just to retain the stored data [15]. While it is theoretically possible to deactivate parts of DRAM not in use, neither software nor hardware provide adequate support for this functionality. Consequently, a substantial amount of power is wasted on maintaining memory that is not actively used.

The missed opportunity for energy savings can be traced back to outdated assumptions that shaped the memory management of the operating systems as we know it today. Modern DRAM devices still offer very few power-saving techniques, applicable only at granularities constrained to specific internal levels of DRAM organization. These granularities are significantly larger than the 4 KiB page frames managed by the operating system. This reintroduces the problem of fragmentation once again: for DRAM deactivation, large contiguous memory segments must be free of useful data. Operating systems are largely blind to fragmentation ("all page frames are equal"), resulting in data being scattered throughout the entire physical memory and thus all memory devices. Furthermore, as the system is running, the page cache continuously grows in size ("only used memory is good memory"). Consequently, in a modern system with considerable uptime, finding an unoccupied DRAM segment that can be deactivated becomes impossible.

#### Contributions of this work

While the underlying reasons for the insufficient support of DRAM power management are deeply rooted in the foundational aspects of contemporary memory management, this work does not aim to redesign it from the ground up; such task would out of scope for a master's thesis. Instead, it proposes a mechanism to revert the damage done by suboptimal memory management. This is achieved by keeping track of the DRAM segments in the system and providing a mechanism to proactively

clear them from used memory. This implements a technique known as *compaction*, where multiple partially used memory chunks are merged into one by migrating their memory contents.

Unlike the existing compaction approaches [11, 7, 8], the mechanism proposed in this thesis is designed specifically with DRAM power management in mind. It supports large granularities of over 1 GiB that are necessary for existing DRAM power-saving modes. Moreover, it incorporates a costbenefit model, that allows it to assess whether the energy spent on cleaning memory segments will be offset their deactivation. To facilitate this assessment, the mechanism scores each segment based on the effort required for its reclamation. This scoring also enables strategic selection of segments for merging that yields the best gains for the minimum effort. Finally, it shrinks the amount of the page cache in the system as part of its operation: since the page cache continually expands and fills all available memory, a mechanism for its earlier eviction is essential for effective DRAM power management.

The thesis consists of five chapters. Following this introduction (Chapter 1), Chapter 2 provides the theoretical foundation necessary to understand the architecture of the proposed mechanism for managing physical memory. Chapter 3 provides a detailed description of the mechanism, starting with a conceptual overview and followed by a description of its implementation in the Linux kernel. In Chapter 4, the mechanism is evaluated in terms of potential energy savings and the performance impact. Finally, Chapter 5 concludes this work and discusses potential areas for future improvement.

FUNDAMENTALS

This chapter provides the theoretical foundation necessary for understanding this thesis. It opens with an overview of DRAM technology in Section 2.1, introducing the internals of DRAM chips and discussing their refresh mechanisms and power-saving modes. The second half of the chapter, Section 2.2, deals with the operating system's memory management, focusing specifically on the intricacies of the Linux memory subsystem. It discusses disk caching, memory reclamation, and memory migration features within Linux. Finally, Section 2.3 closes the chapter with an overview of existing research that intersects memory management with power management.

# 2.1 Dynamic Random-Access Memory

If we examine the components of a general-purpose computer, we will discover a spectrum of different memory technologies. These technologies can generally be graded based on two key qualities that tend to be inversely related: the access time and the price per bit. The latter economic quality also translates to another important characteristic, capacity. As the price per bit decreases, it becomes feasible to use devices with larger capacities. As a consequence, the memory devices in the system range from slow high-capacity memory, such as mechanically rotating hard drives, to fast low-capacity memory, like CPU caches using static random-access memory (SRAM) cells.

This section delves into the technology that serves as a bridge between the two extrema of the speed-capacity spectrum: the *main memory* based on DRAM technology. The designation "main memory" comes from its role in the system—it holds the working set of all applications. The DRAM capacity has managed to scale with ever-increasing memory requirements of applications. For instance, DDR5 modules up to 128 GiB are commercially available [22], with the standard allowing up to 256 GiB per module [23]. Multiple such modules can coexist in a system.

However, the scaling success story of DRAM capacity does not extend to its latency. In the early 1990s, the performance gap between CPUs and DRAM began to widen significantly [24]. This necessitated two drastic changes. Firstly, CPU caches had to grow in size to conceal the high latency of DRAM accesses [24]. Secondly, the DRAM interface started evolving to accommodate high bandwidth demands of larger CPU caches [25]. Unlike early asynchronous DRAM, contemporary devices implement a synchronous (SDRAM) interface, which offers high predictability and enables high throughput via pipelining [26].

Table 2.1 provides an overview of latency and bandwidth of different SDRAM generations. A DDR4 SDRAM takes about 13 ns for a memory access in the best case and up to three times as much in the worst case [27]. Given a 3 GHz CPU clock, this translates to 40 - 120 clock cycles per memory access. For a multicore CPU generating at least one memory reference per core per cycle, such latency is impractical. The CPU cache allows SDRAM to compensate its high latency with its high bandwidth: up to 25.6 GiB/s per channel for DDR4, or over 8 B per clock cycle at 3 GHz. A real system will require much smaller bandwidth due to data and code locality.

| Year | Standard  | Latency [ns] | Module bandwidth [GiB/s] |

|------|-----------|--------------|--------------------------|

| 2002 | DDR1 [28] | 15 – 45      | 3.2                      |

| 2006 | DDR2 [29] | 10 - 30      | 6.4                      |

| 2010 | DDR3 [30] | 13 – 39      | 10.6                     |

| 2016 | DDR4 [31] | 13 – 39      | 21.3                     |

**Table 2.1** – Latencies and bandwidth of different generations of DRAM memory [32]. While the latency has remained constant since over 20 years, the bandwidth doubles with each generation.

#### 2.1.1 Standardization

A major contributor to DRAM's success is its interoperability. The dual in-line memory modules (DIMMs) are the most widespread consumer form of DRAM. These modules, which are just PCBs with DRAM chips and a standard connector, can be purchased off the shelf and installed into a computer's memory slot to improve its performance. This plug-and-play experience is made possible by standardization.

For SDRAM, the standard-governing body is JEDEC Solid-State Technology Association. JEDEC defines three main categories of double data rate (DDR) standards, each tailored towards specific application:

- Main DDR [33] targets laptops, desktops, and servers. The devices in this category come in two form-factors: as a chip soldered onto a PCB or as a replaceable DIMM module.

- Low-power LPDDR [34] devices are found in smartphones, cars, and other embedded applications and include additional power-saving features. Unlike the main DDR standard, LPDDR does not define a DIMM form-factor and these chips are always soldered directly onto the PCB.

- Graphics GDDR [35] standard targets high data bandwidth applications like GPUs and High-Bandwidth Memory (HBM).

While the high level of standardization enables easy interoperability, it is also believed to obstruct innovation [27]. New standards are released once every 5 to 8 years and the process of their ratification is not transparent. It is likely highly influenced by the major DRAM market leaders: Samsung, SK Hynix, and Micron, which collectively control 96.5 percent of the market [36]. The internal workings of DRAM chips remain highly confidential and the body of research on microarchitecture improvements is largely based on speculations [27].

#### 2.1.2 Information Storage

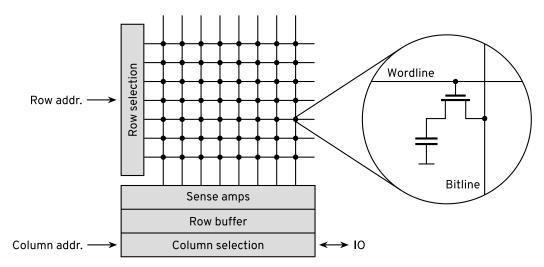

At the core of the DRAM technology lies a cell consisting of a single capacitor and an access transistor. The bit of information is stored in the cell's capacitor in the form of the electric charge. These cells are arranged in a two-dimensional array known as *mat* with horizontal *wordlines* and vertical *bitlines*. Figure 2.1 demonstrates the structure of this array. The wordlines control the gates of the transistors of the whole row. When the wordline is pulled high, the transistor's drain-source channel electrically connects each capacitor to its respective bitline. This results in several peculiarities.

As the bitline is a long conductor that spans across numerous rows of the mat array, it exhibits a high capacitance. When the bitline is connected to the cell's capacitor—a process known as *row opening*—the charge equalization takes place, resulting in a small voltage change on the bitline.

**Figure 2.1** – The DRAM cells consisting of a transistor and a capacitor arranged in a two-dimensional *mat* array [26]. The array is spanned by horizontal wordlines and vertical bitlines.

With a typical 1:6 ratio of cell to bitline capacitance [38], the voltage change on the bitline is under 15 percent.

To interpret this small voltage change, a mat contains a *sense amplifier*. Before the row is opened, the sense amplifier *precharges* the bitline to a voltage level that is midway between logical 0 and logical 1. Doing this allows the sense amplifier to compare the new voltage level of each bitline with the well-defined precharge voltage after the row is opened. The result of this comparison for each bit of row is stored in the *row buffer*.

Note that the charge equalization destroys the information in form of the charge in the capacitor. The capacitor (dis)charges approximately to the precharge voltage when the row is opened. To avoid data loss, the DRAM chip must write the contents of the row buffer back into the cells before another row is accessed. This is achieved by charging each bitline to the voltage representing the

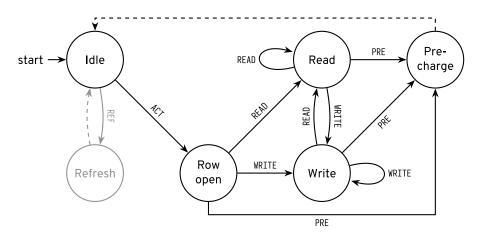

**Figure 2.2** – Simplified state diagram of the chip in the SDRAM protocol [37]. Accessing a cell requires loading its whole row into the row buffer using ACT, allowing subsequent READ and WRITE commands to operate on the contents of the row buffer. The PRE command writes the row-buffer contents back into the cells and precharges the bitlines for the next ACT.

**Figure 2.3** – The hierarchy of the DRAM memory system. In this example, a single channel contains two ranks. Each rank contains four chips, each with four banks inside.

bit stored in the row buffer and activating the wordline. Furthermore, due to the imperfections of the physical implementation, the charge in the capacitors leaks over time. Accordingly, retaining the data requires reading and rewriting (*refreshing*) each row periodically. Section 2.1.4 discusses the specifics of the refresh mechanism in detail.

The SDRAM command interface reflects these characteristics of the mat's operation. Figure 2.2 represents a simplified state diagram of data accesses in SDRAM. In the idle state, the bitlines remain precharged. The ACT command initiates the access by selecting a row and transferring it into the row buffer. The individual bits of the open row are then accessed by providing the column address to the WRITE and READ commands. Before accessing a different row, the protocol demands issuing of the PRE command. This writes the contents of the row buffer back into the cells and precharges the bitlines for the next ACT. Additionally, the refresh of the mat can be requested from the idle state by sending the REF command.

#### 2.1.3 Hierarchy

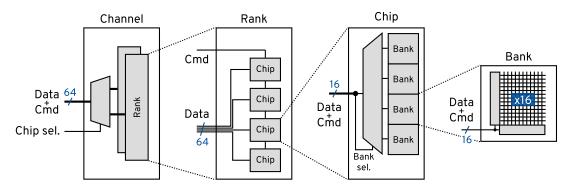

A hierarchical design is essential to enable high capacity and high throughput characteristic to SDRAM. Figure 2.3 provides an overview of the memory system hierarchy with the signal routing. This hierarchy can be divided into two categories: horizontal levels that broaden the memory system's data width, and vertical levels that expand its address space. The mat level, introduced in the previous section, typically falls under the horizontal category. During a memory access, the row and column addresses of the respective commands pinpoint a specific cell in the mat, yielding a single bit of information. However, a single read operation from a DRAM chip can produce more than one bit of data, depending on its  $column\ width$ . The SDRAM column width is represented using notation xN and generally ranges from x4 to x16 [26]. The broad data bus is achieved by stacking multiple mats and addressing them simultaneously, with each mat contributing one bit of data.

The second, vertical, hierarchy level within a chip is the bank level. *Banks* are memory arrays that are addressed independently of each other, with the *bank address* being part of the command. Their independence comes with a performance bonus: it introduces *bank-level parallelism* into the chip's operation [39]. While a single bank is busy processing a command, another bank can be addressed for the next memory access. By interleaving bank accesses through clever address mapping [40–42] or strategic data partitioning [43, 44], the memory system's throughput can be improved significantly. The maximal amount of banks in a chip is defined by the standard, ranging from only four banks in the initial DDR standard [28], to 16 banks in the latest LPDDR5 [34] and

to 32 in DDR5 [33]. DDR4, DDR5, and LPDDR5 further optimize performance by splitting banks into groups and relaxing the timing requirements for memory accesses to different bank groups.

Multiple memory chips that share the command/address bus and the chip select signal collectively form a *rank*. The data pins of the chips within a rank are combined to form a wider data bus. An example of a DRAM rank would be one side of a module's PCB. In consumer modules, the width of the rank data bus is 64 bits (72 bits on RAM with error correction codes), requiring 4 x16, 8 x8, or 16 x4 DRAM chips [45].

The memory controller connects the CPU to the DRAM subsystem and arbitrates CPU's memory accesses. It can have multiple independent channels (recent AMD EPYC processors feature 12 channels [14]), with one or more ranks in each. The chip select signal, shared by all chips within a rank, is used to activate a specific rank in a multi-rank channel. Similar to banks, ranks are independent of each other and introduce a level of parallelism into the memory subsystem [46, 47]. In contrast to bank-level parallelism, *rank-level parallelism* has another trade-off dimension to it. Discrete chips on a PCB require long interconnects transferring data at a high rate. Many ranks in a single channel represent an increased load on the shared transmission lines (e.g., command/address buses connecting to each chip), affecting the maximum operational frequency [26]. *Registered DIMMs (RDIMMs)* mitigate this issue by buffering the signals and reducing the electrical load on the memory controller, allowing more modules per channel.

#### 2.1.4 Refresh Mechanisms

As established in Section 2.1.2, the DRAM cells require periodical refresh to retain data due to inherent leakage currents in the cell. For this, the DRAM standard mandates that each cell must be refreshed once in the *refresh window*  $t_{\rm REFW} = 64\,\rm ms$ . For temperatures over 85 °C, the window is halved to 32 ms. In fact, the majority of DRAM cells hold their contents over much longer time spans [48]. For instance, Baek and associates [49] successfully reduce the refresh rate to 512 ms by identifying weak cells and removing up to 0.1 percent of respective page frames from the operating system's page-frame pool. Nevertheless, the refresh window figure has been chosen conservatively to account for the highest leakage currents occurring due to manufacturing process variations. Furthermore, the cells have also been observed to change their retention period over time [50].

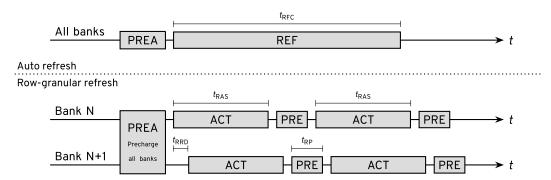

During normal operation, the refresh cycle is managed through the *Auto-Refresh (AR)* mechanism. As the state diagram in Figure 2.2 illustrates, the memory controller issues the REF command to initiate the refresh process. Refreshing the whole chip at once is costly, so the refresh window is split into 8192 *refresh intervals*, each lasting  $t_{\rm REFI} = 7.8$  us. To ensure data retention, the memory controller must issue at least eight refresh commands within the  $8 \cdot t_{\rm REFI}$  period [31]. Technically, a single refresh command refreshes  $N_{\rm rows}/8192$  rows in a round-robin order. The SDRAM device contains an internal counter of refreshed rows that advances with each refresh command [15].

The duration of the refresh command, also known as  $t_{\rm RFC}$ , depends on the device's memory density. For DDR4, it ranges from 160 ns with 2 Gib devices to 550 ns with 16 Gib devices [31]. Thus, the whole rank is not available for  $t_{\rm RFC}/t_{\rm REFI}$  (7 percent for 550 ns) of the time and the memory accesses have to stall. Consequently, refresh comes with a performance penalty and its real cost can be even higher due to the requirement to precharge all banks before refresh and the subsequent row reactivation after refresh.

#### Selective refresh with existing hardware

Until recently, none of the SDRAM standards provided a possibility to selectively refresh portions of memory during normal operation. One way to work around this limitation, is to stop issuing AR

**Figure 2.4** – Commands issued during Auto-Refresh and row-granular refresh [51] and their timing constraints.

| Symbol       | Value [ns] | Name                   | Description                                 |

|--------------|------------|------------------------|---------------------------------------------|

| $t_{ m RAS}$ | 32         | Row Address Strobe     | Duration of the ACT command                 |

| $t_{ m RP}$  | 13.75      | Row Precharge          | Duration of the PRE command                 |

| $t_{ m RRD}$ | 4.9        | Row-to-Row Delay       | Minimum gap between ACTs to different banks |

| $t_{FAW}$    | 21         | Four Activation Window | Timespan in which no more than four activa- |

|              |            |                        | tions are allowed to limit peak current     |

Table 2.2 – Timing parameters of Micron MT40A2G8VA-062E at 3200 MT/s [52].

commands altogether and simulate it by activating the row and then immediately precharging the bank, as shown in Figure 2.4. This has the effect equivalent to a refresh: reading the row into the row buffer and then writing it back again, without the IO transfer overhead.

However, the comparison of REF and ACT+PRE latencies shows the disadvantage of this approach. Consider a DDR4 16 Gib x8 SDRAM device **Micron MT40A2G8VA-062E** [52] operating at the highest data rate. It contains  $2^{17}$  rows, each 1 KiB wide. Thus, a single refresh command handles  $2^{17}/8192=16$  rows in all 16 banks at a time and takes  $t_{\rm RFC}=350\,\rm ns$  to complete. On the other hand, to perform the equivalent ACT+PRE sequence, the memory controller must respect the timing parameters shown in Figure 2.4 and Table 2.2. Even ignoring the four activation window  $t_{\rm FAW}$  this requires twice as much time:

$$(N_{\text{banks}} - 1) \cdot t_{\text{RRD}} + \frac{N_{\text{rows}}}{8192} \cdot (t_{\text{RAS}} + t_{\text{RP}}) = 805.5 \,\text{ns}$$

(2.1)

Although explicit row opening achieves selective refresh on the granularity in the ballpark of memory paging (explained in Section 2.2), it appears exceedingly inefficient. This hints that the internal implementation of the Auto-Refresh is highly optimized and the optimized mechanisms are not exposed through the SDRAM interface—at least when operating within the specification.

Mathew *et al.* [51] investigate this experimentally and discover that by reducing the SDRAM timing parameters (i.e., violating the specification) the overhead of row-granular refresh can be reduced without the loss of reliability. The DDR3 device under test has 16384 rows and thus refreshes two rows per refresh command, which takes 262.5 ns to complete. Two equivalent ACT+PRE issued for each bank in parallel (2 rows  $\times$  8 banks = 16 commands in total) require 292.5 ns according to the specification. With relaxed timing, the duration of the manual refresh reduces to 146.25 ns, 44 percent less than Auto-Refresh. The energy figures are promising as well: while the optimized

row-granular refresh still uses more energy than a full AR, it is enough to omit refresh for just 10 percent of the memory to break even. Due to the out-of-spec operation, the success of this technique may vary from device to device and relies on low amount of rows.

LPDDR2+ standards provide a *per-bank refresh* command REFpb. Initially, this command refreshed a single bank in a round-robin manner with an internal bank counter. In LPDDR4 and later, the command encoding reserved a few bits to specify the bank address, allowing the memory controller to schedule bank refreshes in an arbitrary order. Similarly, DDR5 gained a *same-bank refresh* command REFsb, allowing refresh of bank groups in any order. However, the standard forbids issuing this kind of refresh command to the same bank (or bank group in DDR5) unless all other banks (bank groups) have been refreshed, making selective refresh on the bank granularity using these commands illegal. Perhaps also here energy and performance improvements can be achieved by violating the standard. To the best of my knowledge, no works have attempted this yet.

Finally, the LPDDR5 [34] standard introduces Partial-Array Refresh Control (PARC), a mechanism previously described in a 2017 Qualcomm patent [53]. Both documents advertise the new feature as a way to reduce refresh power consumption. PARC splits banks into eight segments and uses an 8-bit bitmap register to mask the refresh operation within the specific segment of all banks, providing a way to reduce refresh power consumption during normal operation applicable on the 1/8 rank granularity.

#### Proposed selective refresh mechanisms

The first suggested but never actually implemented technique for selective refresh of DRAM, *Selective Refresh Architecture (SRA)* [54], dates back to 1998. It proposes introducing a bitmap that allows toggling refresh per row. Cui *at al.* [55] survey hardware- and software-based refresh reduction techniques and use the results to design their *DTail* mechanism. Extending SRA, their proposal features a 4-bit register for each row that can be used to either disable refresh altogether or to extend the refresh window beyond the standard 64 ms. These mechanisms come with significant memory and chip area overhead and are thus unlikely to be adopted by future standard versions.

Seeking to modify the hardware as little as possible, *Flexible auto-refresh (REFLEX)* [56] utilizes the fact that DRAM chips include an internal counter of recently refreshed rows that is advanced on each refresh command. The authors propose exporting this counter to the memory controller along with a "dummy refresh" command that increments the counter without performing any actual refresh operations. In a similar vein, Jafri and colleagues propose *Partial Array Auto-Refresh (PAAR)* [57], a refresh reduction technique in two variations: (1) the bank-granular version with minimal hardware modifications resembling PARC and (2) a version with a register containing an address range that will be refreshed on auto refresh. Their primary contribution is the algorithm to bypass refresh of accessed rows in an application with a predictable access pattern (e.g., a convolutional neural network). Indeed, as memory accesses have a side effect of refreshing the row, such rows need not be refreshed if accessed frequently. Utilizing this fact, *Smart Refresh* [58] introduces counters into the memory controller to track recent accesses and skip the refresh accordingly.

#### 2.1.5 Power-Saving Modes

SDRAM devices feature several power-saving modes that can be entered during periods of inactivity. The *Self-Refresh (SR)* mode disables most of the clock circuitry and the external IO. In this mode, data is retained by internal timers triggering refresh without the intervention of the memory controller. To reduce the standby current further, data retention can be disabled for specific memory regions by setting the *Partial-Array Self-Refresh (PASR)* register before entering Self-Refresh. Notably, the same segment mask is utilized for both PASR and PARC in LPDDR5. Although the PASR feature is

mandatory in all LPDDR standards, it was optional in DDR2 and DDR3. The DDR4 standard does not include PASR and it is officially deprecated in DDR5 due to security concerns [59], which suggests that its low-power sibling PARC is unlikely to appear in the future DDR standards.

When examining power-saving modes and in particular the hierarchy levels they apply to, it is important to consider the *on-die termination (ODT)*. The memory subsystem includes long off-chip interconnects as traces on a PCB. When transferring signals at a high rate, the interconnect has to be analyzed as a transmission line. Any nonuniformities within the impedance of the transmission line cause reflections and distort the signal, affecting the maximum frequency [60]. To combat this challenge, the DRAM chips include a configurable (34 to 240  $\Omega$  or Hi-Z when off in DDR4) impedance on the die. While ranks can independently enter any power-saving modes, some of the modes (including Self-Refresh) disable ODT. This makes their application at this level impractical: by disabling the termination of a single rank, the whole channel suffers from resulting reflections and the transfer rates plummet.

Another power-saving mode disabling ODT is the DDR4's *Maximum Power Saving Mode (MPSM)*. In principle, MPSM is a variation of Self-Refresh without any refresh activity. Thankfully, DDR5 introduces a variation of MPSM that retains ODT and is applicable at the rank level. Moreover, all DDR and LPDDR standards support idle *Power-Down* mode that is entered when the *clock enable (CKE)* signal is asserted low. This mode keeps the ODT and exhibits very quick entry and exit latencies (7.5 ns). As a result, it can be exited periodically to send refresh commands and retain data. In fact, some standards limit the maximum duration of Power-Down to the refresh interval [34]. Table 2.3 presents a summary of power-saving modes along with entry/exit latencies and estimated potential power savings for an exemplary DDR5 memory system featuring eight 16 Gib **Micron MT60B4G4** devices in a rank.

# 2.2 Operating Systems

Modern computers of any scale—from smartphones to supercomputers, and even some embedded systems—rely on *virtual memory*. Virtual memory allows abstracting the address space of the main memory of the system into one or several *virtual address spaces*. The modern implementations of virtual memory use *paging*. With paging, the physical address space is divided into equally-sized page frames (typically 4 KiB). In the exact same way, the virtual address space is divided into pages.

| Power mode         | Granularity      | Power savi   | ng [mW/GiB]    | Latency | DDR<br>1 2 3 4 5 | LPDDR<br>1 2 3 4 5 |

|--------------------|------------------|--------------|----------------|---------|------------------|--------------------|

| Full ch. power off | Channel          | 82.8         | (100 %)        | >25 ms  | ব্ৰব্ৰব্ৰ        | ব্ৰ্ব্ৰ            |

| Self Refresh       | Channel          | 0.53         | (0.6%)         | 640 ns  | ব্ ব্ ব্ ব্      | व्य व्य व्य व्य    |

| MPSM               | Channel          | 22.95        | (27.7%)        | 640 ns  | ব্ ব্ ব্ ব্      |                    |

| MPSM (DDR5)        | Rank (16 GiB)    | 15.97        | (19.1%)        | 21.5 ns |                  |                    |

| Power-Down         | Rank (16 GiB)    | 14.6         | (15.6%)        | 7.5 ns  | ব ব ব ব ব        | र्व र्व र्व र्व    |

| PASR               | 1/8 Rank (2 GiB) | 0.53 - 22.95 | (0.6 – 27.7 %) | 640 ns  |                  | ব্ ব্ ব্ ব্        |

| PARC               | 1/8 Rank (2 GiB) | 0 – 9.19     | (0 – 11.1 %)   | 14 ns   |                  |                    |

**Table 2.3** – Power-saving modes of all standards with their granularity, estimated power savings, and latency for a 16 Gib Micron MT60B4G4 [61].

Using a translation mechanism, like a page table, the dedicated hardware *Memory Management Unit (MMU)* maps the virtual pages to physical page frames transparently on each memory access.

The details of the translation mechanism are not essential here; instead, we outline its key characteristics. Firstly, the translation mapping is **dynamic**: it can be modified at runtime or completely swapped out for another one. By switching the mapping on program scheduling, the OS provides each application with its own virtual address space. Incidentally, this results in **isolation**, as the applications can only access memory that has a mapping in their virtual address space. This guarantees that programs do not interfere with each other's data unless explicitly allowed via a shared memory mechanism.

Secondly, virtual memory effectively **conceals fragmentation** of physical memory. Even if the application's physical page frames are scattered throughout the main memory, the translation mapping allows the OS to present them at an arbitrary virtual memory location in any order, or even as a contiguous memory region. And lastly, the operating systems use virtual memory to implement other **virtualization** techniques. For example, this allows the OS to defer memory allocations until they are actually needed or to transparently present other storage media as memory. These techniques are implemented by providing a *page-fault handler*, a routine that gets called when the process accesses unmapped memory.

#### 2.2.1 Page-Frame Allocator

To manage physical page frames, the operating systems utilize a *page-frame allocator*. Its task is to manage the pool of unused and available page frames and to provide them to OS subsystems or applications on demand. Once the requesting thread finishes using the page frame and *frees* it, the allocator adds the released page frame back to its reserves. A common allocator design, also employed by the Linux kernel, is the *buddy allocator* [62, 63].

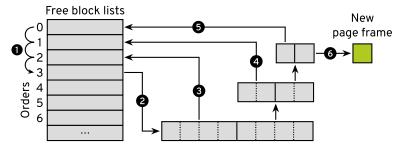

The buddy allocator maintains several lists of free contiguous naturally-aligned blocks, one list for each block size. The block sizes are limited to power-of-two multiples (*orders*) of the basic unit of memory management: a single page frame. Thus, there are separate lists for contiguous blocks of sizes 4 KiB ( $2^0$  frames), 8 KiB ( $2^1$  frames), 16 KiB ( $2^2$  frames), and so on. In Linux, the maximum tracked order is 10 or  $2^{10} \cdot 4$  KiB = 4 MiB in size.

When a contiguous memory block of the specific order is requested, the buddy allocator first checks the corresponding list for an available block. If the list contains a free block of the requested size, it is removed from the list and returned to the caller. Should the list contain no such block, the allocator proceeds to check the list for the next higher order. This ascending process continues until a free block larger than the requested size is found. Once a suitable block is located, it is isolated from the list and the *splitting* begins.

Having isolated the block larger than the requested size, the allocator splits it into two equally-sized *buddies*. One of the buddies is placed on the next lower list corresponding to its halved size and the other buddy is used for further splitting. If the block is still bigger than requested, the process is recursively repeated until it reaches the desired size. At that point, the memory block is returned to the caller and all its former buddies reside on the respective lists. The *merging* is the reverse operation of splitting. When a block is freed, the respective list is checked for its buddy. If the buddy is present (i.e., together they form a naturally-aligned contiguous block), they are melted together into a single next-order block. The lists are recursively ascended until no melting is possible and the resulting block is stored on the list.

Figure 2.5 illustrates the working principle of the buddy allocator by example. In this case, a zero-order page frame is requested. Queries on zero-, first-, and second-order lists return no suitable

blocks ①, only the third-order list returns a block consisting of eight page frames ②. The block is split into two four-frame blocks, with one half put back on the second-order list ③, and the other half used for further splitting. The process is repeated for the four-frame block ④ and the two-frame block ⑤. The result is a single page frame, which is returned to the caller ⑥.

#### **Pageblocks**

By maintaining page frames as contiguously as possible, the buddy allocator proves to be effective against *external fragmentation*: scattering of blocks throughout the physical address space [64]. However, based on the observation that single page frames are much more frequently requested than higher-order blocks, Linux optimizes such allocations by employing *per-CPU page-frame caches* [65]. Each such cache contains some page frames that are instantly returned for page-frame requests by the local CPU core. In Linux 5.13, the cache was extended to other common orders. Unfortunately, this optimization eliminates the defragmenting character of the buddy allocator by delaying merging operations and complicating defragmentation heuristics [66, 10].

Huge frames or order 9 (2 MiB) blocks have a particularly high value for the memory management. Along with 4 KiB page frames, they can be used for virtual address mappings on all major architectures [67, 68]. Such mappings put less pressure on the address translation mechanism and exhibit better performance [5]. To counteract the effect of the per-CPU caches and attain huge frames, the Linux kernel introduced *pageblocks*. In a nutshell, the pageblock mechanism assigns a *migrate type* to each huge frame in the system. The migrate type categories indicate the mobility of the memory contained in the huge frame:

- MIGRATE\_RECLAIMABLE if it can be freed quickly,

- MIGRATE\_MOVABLE if it can be moved,

- MIGRATE\_UNMOVABLE for immovable memory, like kernel allocations,

- and several others reserved for special cases.

The Linux buddy allocator maintains separate free-block lists for each order and for each migrate type. Keeping track of this information and separating the free lists enables the Linux kernel to place new allocations (which indicate their planned mobility) in the respective pageblocks, grouping allocations with the same mobility together. This grouping makes active defragmentation described in Section 2.2.3 more effective.

#### **Nodes and Zones**

The Linux kernel memory management supports Non-Uniform Memory Access (NUMA). NUMA systems feature different access latencies to different regions of memory, depending on the CPU core that performs the access. For example, the CPU may access its local memory quickly, but it

**Figure 2.5** – Example allocation of order 0 with the buddy allocator. The algorithm finds no suitable blocks in lists for orders 0, 1, and 2. The order 3 block is split thrice to acquire a single page frame.

also might access memory of another CPU with additional performance penalty. In such systems it is desirable to pin applications and their memory to a particular CPU and its local memory, where it benefits from fast accesses. To implement this, Linux splits memory into *nodes*.

The nodes are split once again into *zones*. Each zone hosts its own allocator instance with its own free lists and bookkeeping. This division enables allocations with special physical address requirements. For example, ZONE\_DMA/ZONE\_DMA32 contain the first 16 MiB/4 GiB of memory and are used to allocate memory shared with devices that have that kind of addressing constraint. The rest of allocations fall into ZONE\_NORMAL. The optional ZONE\_MOVABLE zone, which is disabled by default, splits the node into another region reserved for movable allocations, making compaction (Section 2.2.3) even more effective. Immovable kernel allocations are not allowed in the movable zone and are directed to other zones. On the other hand, movable allocations may fallback to other zones if the movable zone is full [69].

#### 2.2.2 Disk Caching

The concept of virtual memory was initially developed in response to the limited memory resources available in the early days of computing [1]. With low amount of memory at hand, the programmers who needed to use more memory than the primary, directly-addressable storage could provide had to design their algorithms accordingly. This involved tedious swapping of sections of program data in the primary storage with sections located in the secondary storage (e.g., disk). Wishing to relieve the algorithm designers of this burden, the OS and hardware designers came up with a technique that makes accesses to the secondary storage transparent [3].

While the primary storage no longer poses a significant constraint for most program workloads, virtual memory is still used to abstract secondary storage. When a user program accesses a file on a disk for the first time, the OS loads the file contents into RAM and adds it to the *page cache*. Subsequent file accesses then utilize this cached copy, allowing for faster access times. The cache pages can also be mapped into the program's virtual memory mapping, virtualizing disk contents as a regular memory region. If the program modifies the file, the changes are not propagated to the disk immediately. The *writeback* is deferred in case the data is modified again in the near future. The page is said to be *dirty* if it contains unwritten content. Furthermore, even after the program has terminated or finished its file operations, the associated pages remain in the page cache in case the file is opened again.

This design is based on two assumptions: (1) disk accesses are prohibitively slow, and (2) free memory is wasted memory. Indeed, the access latency for hard drives typically falls within the millisecond range [70, 71]. Incurring such latency on each file access would render the system unusable. However, the advent of SSDs, which offer random-access latencies in microseconds [72] challenges this assumption. Moreover, unlike hard drives, SSDs can service multiple parallel requests efficiently, resulting in much higher throughput. In fact, the current Linux memory management subsystem, originally designed for HDDs, has been identified as too slow to fully utilize the high bandwidth offered by modern SSDs [73]. The second assumption that unused memory is a *stranded asset* [74] is reinforced by the fact that none of the power-saving modes described in Section 2.1.5 are utilized on consumer systems. This is partly due to the lack of support from operating systems and memory controllers for these features.

#### Page-frame reclamation

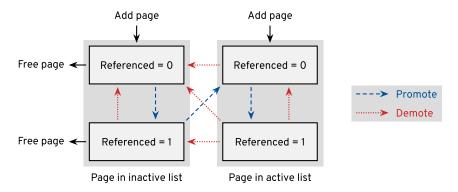

With the memory usage growing constantly due to disk caching, the memory reserves eventually deplete. Thus, the OS requires a mechanism to evict some of the pages to make room for new allocations. The Linux page-frame reclamation algorithm (PFRA) is commonly referred to as the LRU

Figure 2.6 – The states assigned to pages within the Linux page-frame reclamation algorithm.

(least recently used) mechanism. However, this is not strictly true, as Linux does not maintain an LRU-ordered list of page frames [75]. Instead, Linux implements a simplified version of the 2Q algorithm [76].

The algorithm differentiates between two page types: anonymous (program memory not associated with a file) and file (page cache). For each page type, the algorithm maintains two lists per page type: the *active* and the *inactive* list. Under memory pressure, the lists are iterated and all the pages are checked for references. To check the page for references, the kernel utilizes the *reverse mapping*, which returns all virtual address spaces that map the page. In the mapping structures of the virtual address space, the MMU provides the *accessed* bit that is set transparently by hardware when a memory access to the page is detected.

By checking and resetting the accessed bit in each mapping, the kernel can determine whether the page has been accessed by the user process since the last scan. This information is then used to either promote the page to the active state, or to demote it to the inactive state. When the page is already inactive and has not been referenced, it is freed. To add some inertia to this mechanism, the page frame descriptor (struct page) stores another *referenced* bit, representing whether the page has been classified as accessed on the last scan. Figure 2.6 demonstrates the states that the page can assume and the possible transitions.

#### 2.2.3 Page Migration

The internal Linux kernel interface provides functions for memory migration. These functions can be used to move contents of a set of source page frames into another set of destination page frames. More importantly, the migration functions also take care of all the mappings referencing the source page frames, allowing migration of pages that may be concurrently used by applications. Apart from the NUMA support, the two major subsystems making use of the migration infrastructure are *compaction* and *hotplugging*.

#### Compaction

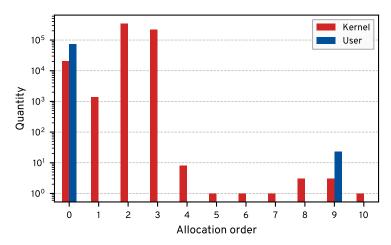

As briefly mentioned in Section 2.2.1, contiguous naturally-aligned blocks of physical memory are a valuable resource to the memory management subsystem of the OS, as they can be used for huge 2 MiB frames. Moreover, as the kernel primarily uses a fixed identity mapping of the physical memory, all its internal allocations have to be contiguous. As shown in Figure 2.7, over 90 percent of the kernel allocations fall within the 16 - 32 KiB range and allocations as big as the maximum size of  $2^{10}$  page frames or 4 MiB are not uncommon [66].

**Figure 2.7** – Requested allocation sizes (logarithmic) during system startup and a 120-second Memcached benchmark [66].

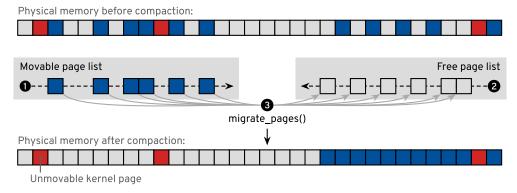

To defragment the memory and gain such contiguous blocks, Linux employs active compaction. The compaction can be triggered either manually by the user, proactively by the kernel, or when an allocation of a large size fails [77, 78]. Figure 2.8 demonstrates the algorithm by a simple example. At the beginning, two iteration cursors are placed: one at the beginning of the zone and the other at the end of the zone. Then, iterating through the pages at the beginning of the zone, the algorithm accumulates movable pages that it encounters in the *movable list* ①. As optimization, compaction checks the migrate type assigned to the pageblock (4 MiB) and skips it completely if it indicates immovable pages. Meanwhile, the second part of the algorithm works from the end of the zone, moving toward lower addresses, and adding free page frames to the *free list* ②. Eventually the two cursors meet or enough movable pages have been collected to satisfy the failed allocation. At that point, the migration routine is called to migrate all the movable pages into the accumulated free page frames ③.

The presence of kernel pages makes compaction less effective. Unlike user pages, which can be relocated by adjusting the mapping structures of the processes, kernel pages are generally immovable. This immobility renders the entire block unreclaimable to the defragmentation algorithm. Although the Linux kernel does have a mechanism for movable kernel pages [79], it requires explicit

**Figure 2.8** – The Linux compaction algorithm. The algorithm collects movable pages from the beginning of the zone and migrates them into free page frames at the end of the zone.

support from the subsystems. As of Linux 6.1, only two drivers (z3fold and zsmalloc) provide the necessary callbacks to relocate their pages.

#### **Memory Hotplugging**

Linux supports *memory hotplugging* [80], enabling removal of memory from the system at runtime. To avoid system crashes or data corruption, the administrator must ensure that no data currently in use by the OS or user applications resides on the memory device (e.g., a DIMM) before physically disconnecting it from the system. The hotplugging infrastructure facilitates this, providing an interface to *offline* specified memory regions.

Technically, memory hotplugging divides the memory node into contiguous blocks of fixed size depending on build-time configuration. On x86-64, these blocks are typically 128 MiB in size. Each block is presented as a separate device in /sys/devices/system/memory. If the user requests offlining by writing into the respective file, the kernel first iterates through the pageblocks (see Section 2.2.1) in the range and sets their migrate type to one of special types, MIGRATE\_ISOLATE. As each migrate type has its own set of free lists within the buddy allocator, this has the effect that concurrently freed pages within the range end up on the MIGRATE\_ISOLATE lists. These lists are never used by the buddy allocator.

Having isolated the pageblocks, the mechanism iterates through the individual page frames in the range. If the page frame is in use, it is migrated to a page frame outside the offlining range. In this case, the source page frame automatically ends up on the isolated lists of the buddy allocator after it is freed by the migration routine. The pages within the range that are already free are manually moved to the isolated lists. Finally, with all pages being removed from the allocator's pool, memory hotplugging adjusts the bookkeeping structures and returns. Memory *onlining* performs the reverse operation: it populates the allocator's free lists with the new page frames and sets all the pageblocks within the range to MIGRATE\_MOVABLE.

Just like with compaction, the presence of an immovable kernel page within the range makes its offlining impossible. Because of this reason, the Linux documentation suggests enabling ZONE\_MOVABLE (which is typically disabled) to increase the likelihood of successful offlining [80].

#### 2.3 Related Work

As shown in Section 2.1.4, numerous works have raised the subject of energy-efficient memory management and proposed novel hardware mechanisms. However, a gap remains in the collaboration between the OS and the hardware to address this issue effectively. This section provides an insight into how different studies have attempted to tackle this challenge.

#### **OS-based DRAM power management**

ESKIMO [81] is the first work to propose disabling the DRAM refresh for unused memory regions. They base their work on SRA [54], a proposal to introduce a bitmap for toggling refresh on a perrow basis. To track unused memory regions, the authors modify the C standard library functions malloc() and free(). They simulate their approach using the DRAMsim simulator [82] and observe up to 86 percent energy savings.

Baek and colleagues [49] recognize that the OS already possesses the necessary information at row-level granularity. Consequently, they integrate their mechanism into the Linux kernel and evaluate it on single-board ARM computers, specifically the BeagleBoard [83] and PandaBoard. To circumvent the lack of selective refresh in existing hardware, they simulate row-granular refresh by (1) disabling the hardware Auto-Refresh and (2) introducing a software real-time thread

that refreshes used rows by performing reads on them. Given the inefficiency of this arrangement, they do not provide energy measurements. Instead, they demonstrate that selective refresh at a row granularity can reduce refresh operations by as much as 93.8 percent on average, and that the OS support at such fine granularities is trivial. Additionally, they propose to mask page frames containing weak DRAM cells in the OS, allowing for reduced refresh rates and thus demonstrating performance improvements.

*GreenDIMM* [84] proposes a deep power-down state in the DRAM at sub-array (128 – 512 MiB) granularity that comes with Linux support. The OS power manager monitors the memory utilization and employs memory hotplugging to clear randomly selected blocks before transferring them into the power-down state. Having no block selection policy, this technique does not account for the trade-off between the cost of offlining blocks and the potential energy savings achieved.

#### Fragmentation and its costs

There is an extensive body of research dedicated to maximizing the benefits provided by huge pages [9, 6–8, 85, 86, 11]. Much like with DRAM power management, the OS is faced with a dilemma whether it is worth investing processor cycles to construct a huge-page mapping *before* the future performance benefits can be known. *MEGA* [11] is a compaction mechanism that, unlike built-in Linux compaction, monitors both the occupancy levels of huge frames and the age of the pages within them. This information is then used to make a cost-benefit analysis before compacting. In a similar vein, Mansi *et al.* [87] introduce a policy into the Linux virtual memory management that employs an empirically-based cost-benefit model to determine whether the performance benefits of a huge-page mapping outweigh the associated costs.

While blocks larger than huge frames may not be as widely discussed, there are still some studies that emphasize their importance. On mobile systems, external devices such as the video camera may suddenly demand large contiguous blocks. To meet these requests, the prevalent approach is to reserve this memory in advance, resulting in resource underutilization. Seeking to make the reserved memory useful, the *rental memory* approach [88, 89] restricts the pages allocated within these reserved blocks to pages that can be quickly and easily evicted, such as page cache. Essentially, the device's memory is temporarily borrowed by the kernel to store quickly reclaimable data.

Alverti and associates [90] seek to alleviate address translation overhead in virtualized environments by employing large contiguous blocks. Their approach, termed as *contiguity-aware paging*, is a modification to demand paging that attempts to use physically contiguous pages for virtually contiguous mappings (VMAs). They have noted that this technique has a side effect of slowing down fragmentation development by physically grouping pages with similar lifetimes. The same effect is observed by Kim *et. al* [91], who implement memory management on mobile devices that groups pages with the same deallocation time in contiguous regions.

ARCHITECTURE 3

This chapter describes the implementation of the thesis. It starts by introducing the theoretical concepts behind the mechanism in Section 3.1. Then, it moves on to the technical details of the practical implementation in Section 3.2. Finally, Section 3.3 outlines the limitations of the implementation and proposes solutions to address them in the future.

## 3.1 Concept

When it comes to managing DRAM power, there is a substantial gap between software and hardware. As illustrated in Table 2.3, the power-saving modes supported by contemporary DRAM chips are restricted to coarse granularities exceeding 1 GiB. The mode with the finest granularity, PARC was introduced only recently in LPDDR5. Although systems incorporating LPDDR5 memory are now commonly available, current CPU memory controllers still do not provide software access to PARC. Not surprisingly, my extensive search has failed to yield any examples of PARC being applied in practice.

On the other side of the gap, operating systems lack any infrastructure that would facilitate usage of DRAM power-saving modes with coarse granularities effectively and the previous attempts to build such infrastructure were ultimately abandoned [92]. This situation presents a classic chicken-and-egg problem: hardware developers are reluctant to incorporate these features into DRAM and memory controllers without existing software support, yet such support is hindered by the absence of corresponding hardware features. The objective of this work is to tackle this issue from the software perspective by developing a comprehensive framework to support both existing and emerging DRAM power-saving modes within the operating system.

For brevity, I refer to DRAM segments capable of entering power-saving modes as *slices* and the process of transitioning them into a low-power state as *offlining*. More precisely, the required OS support would entail (1) the identification of unused slices, (2) communication with the memory controller to offline them, and (3) the possibility to clear partially used slices with the goal of saving energy. The first two requirements are a matter of introducing additional bookkeeping into the OS memory management and providing hardware-specific drivers. However, effectively implementing the third requirement is more complex; it necessitates evaluating the costs and benefits of the operation before proceeding.

Depending on the physical-to-DRAM address mapping, the slices may either be fully contiguous or consist of smaller contiguous segments distributed throughout the physical address space in a regular pattern. As a long as each slice maps to a subset of the physical memory consisting of complete page frames, there is a potential for energy savings. Given that the address mapping is determined solely by the memory controller, this work assumes a configuration that maps every slice to a single contiguous region in physical memory. It is reasonable to expect that if future memory controllers provide software access to slice power management, they will offer a (configurable) address mapping that makes this feature practical. Nevertheless, the presented concepts are just as well applicable to mappings with noncontiguous slices.

#### 3.1.1 Understanding Fragmentation

Organizing data to retain large contiguous blocks of memory free is referred to as *defragmentation*. Most defragmentation efforts in the systems software research are directed towards supporting huge pages, both via passive *fragmentation avoidance* [90, 91, 9] strategies and active *compaction* [11, 7, 8] mechanisms. However, the passive allocation strategies that attempt to keep large contiguous blocks of memory free can at most *delay* the fragmentation. Eventually, the memory becomes cluttered and no allocation strategy can revert this process. To see why this is the case, it is important to understand the source of external fragmentation in main memory. It occurs when pages with different lifetimes get intermixed. As the short-lived pages get deallocated, holes in rather allocated regions appear. In an attempt to reduce fragmentation, the allocator fills these gaps with newly allocated—potentially long-lived—pages. If the memory utilization sinks, the short-lived pages eventually cease to exist but the long-lived pages remain scattered throughout the memory, rendering large contiguous blocks unusable for slice offlining or huge page-frame allocation.

An ideal allocation strategy clusters pages with similar lifetimes together. This approach would lead to large contiguous blocks of free memory following their nearly simultaneous deallocation. However, allocators lack information about the lifetimes of pages because neither user programs nor kernel subsystems provide such data at allocation. Assuming that programs do not interact with the outside world (e.g., user), retrieving this information generally requires solving the halting problem, as the last possible time at which an anonymous page is deallocated is the program termination. Without this information, the page-frame allocators can only work with heuristics, inevitably intermixing pages with different lifetimes to some extent. There is no free lunch in defragmentation: eventually it is up to compaction to actively revert the clutter via page migration.

#### 3.1.2 Optimal Compaction

To achieve optimal compaction, the target block size must be known ahead of time. For instance, the Linux kernel compaction tends to invest excessive effort for the given gain in free blocks of the desired size. Its size-agnostic design enables simple implementation without requiring additional bookkeeping. The simplicity alleviates the extra cost, which stays within acceptable bounds for relatively fine granularities of 2 MiB. However, for the coarse RAM slice granularities, this approach is impractical.

Specifying the target size allows the compaction mechanism to analyze the memory utilization beforehand and calculate a score for each slice using a metric that reflects the effort required to reclaim it. Based on these scores, the algorithm can make informed decisions regarding two variables of memory migration: the source and the target. Aiming to maximize the benefit relative to the cost, the algorithm selects slices that require the least effort as the migration source. Conversely, the optimal target for memory migration are the *nonfull* slices that would require the most effort to free, as they are least likely to become the migration source. This approach results in the maximum fragmentation reduction for a given block size [61].

#### Page cache

In the context of compaction for DRAM power-saving, the page cache represents a double-edged sword. On the one hand, its pages remain allocated until they are evicted due to memory pressure. Thus, they are the prime example of the long-lived pages that fill the holes and get thereby scattered through the memory, causing fragmentation. On the other hand, unused (i.e., not mapped into applications) and clean (i.e., containing no unwritten changes) cache pages are easy to remove: they require no migration and can be simply discarded. Nevertheless, this removal comes with a

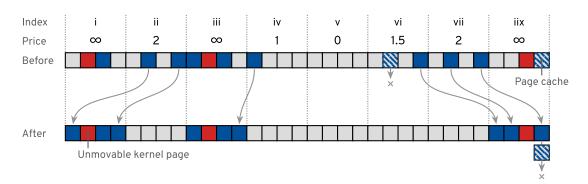

**Figure 3.1** – The optimal compaction algorithm with special handling of cache pages. The memory is split into 4-page slices and each slice is assigned a reclamation price. The algorithm moves pages from the cheapest slices into the most expensive, freeing unused cache pages in the process.

caveat: if these pages are accessed again later, the removal incurred delayed costs associated with reloading the data from the backing storage. For slice offlining, however, shrinking the page cache is a necessity as it eventually fills the whole memory and prevents potential energy savings.

This distinction between different page types also complicates construction of the slice metric for optimal compaction. The hidden costs of page cache removal cannot be known ahead of time. Moreover, the cache pages can be freed in the target slice and thus become potential migration destinations, increasing compaction effectiveness. However, the single reclamation effort metric is no longer sufficient to optimally determine the target migration slice. The algorithm also needs to consider the cost and benefit of allocating pages in the destination slice. For instance, the destination slice containing n free page frames should be preferred to a slice containing n freeable cache pages: it provides equal benefit for less cost.

Figure 3.1 illustrates the algorithm on the example arrangement used in Figure 2.8 previously. The physical memory is divided into four-page slices and each slice is assigned a reclamation price. The price is equal to the amount of movable pages in the slice, while a freeable cache page counts as half a page. Slices that contain unmovable pages are assigned infinite price. The compaction reclaims four slices in total, requiring six migrations and two frees in the process. It also includes special handling of the page cache: the unused cache page in slice vi is freed instead of being migrated. Similarly, the cache page in the last slice iix is freed to accommodate a movable page from slice vii.

# 3.2 Implementation

The described algorithm is implemented in the Linux kernel version 6.1. Hereinafter, this implementation of the algorithm is called *Ramslice*. Overall, the changes span over 28 source files, all of which are in the memory management subsystem. The modifications in existing files are nonintrusive, minimal, and do not exceed few lines. The heart of the algorithm is self-contained in its own source file, which spans just over 1200 (+200 for the respective header file) significant lines of code.

| Symbol           | Name            | Description                                        |

|------------------|-----------------|----------------------------------------------------|

| $N_{ m free}$    | RSI_FREE        | Amount of free page frames                         |

| $N_{ m lru}$     | RSI_V_LRU       | Amount of pages in all LRU lists (userspace pages) |

| $N_{ m anon}$    | RSI_ANON_MAPPED | Amount of anonymous pages                          |

| $N_{ m filemap}$ | RSI_FILE_MAPPED | Amount of file pages mapped into userspace         |

| $N_{ m fileall}$ | RSI_FILE        | Total amount of file pages                         |

| $N_{ m maps}$    | RSI_MAPPINGS    | Total sum of userspace mappings for all pages      |

**Table 3.1** – Per-slice statistics tracked by Ramslice. These counters are used to calculate the amount of freeable, movable, and unmovable pages in the slice and determine its reclamation price.

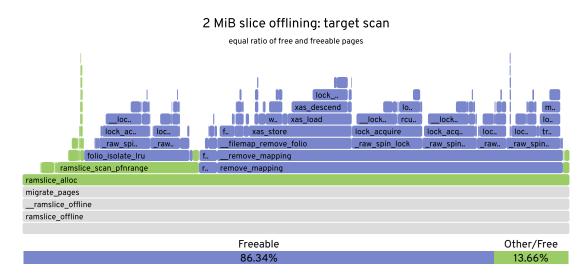

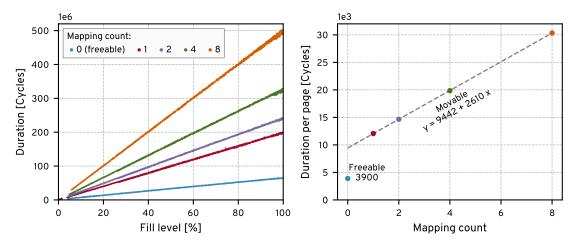

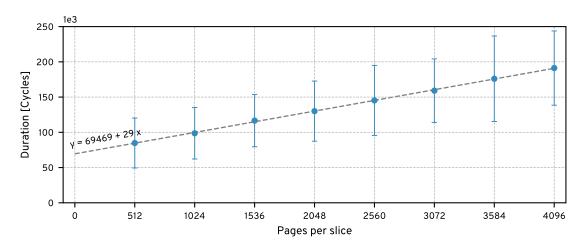

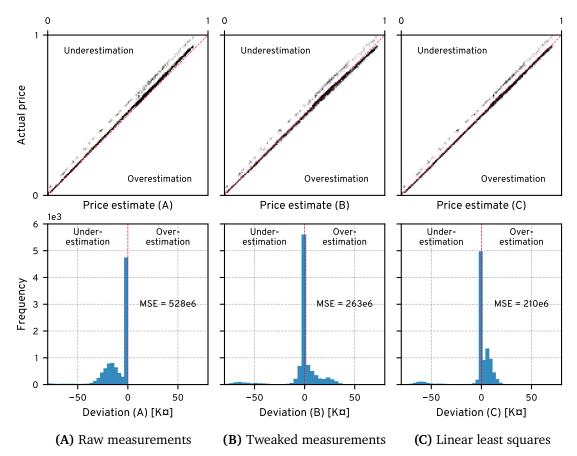

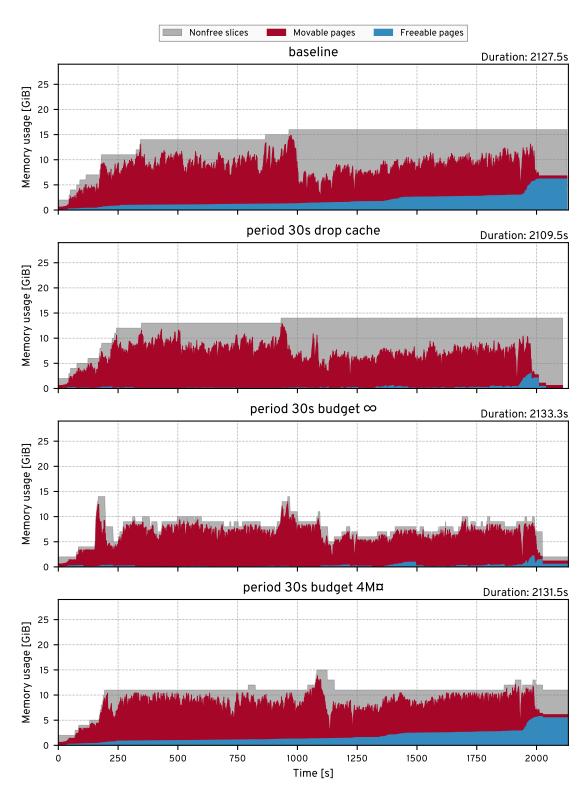

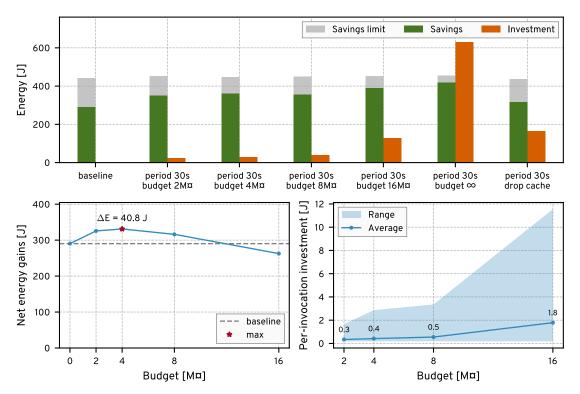

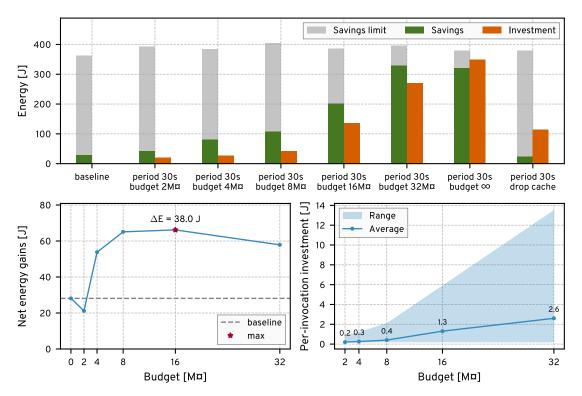

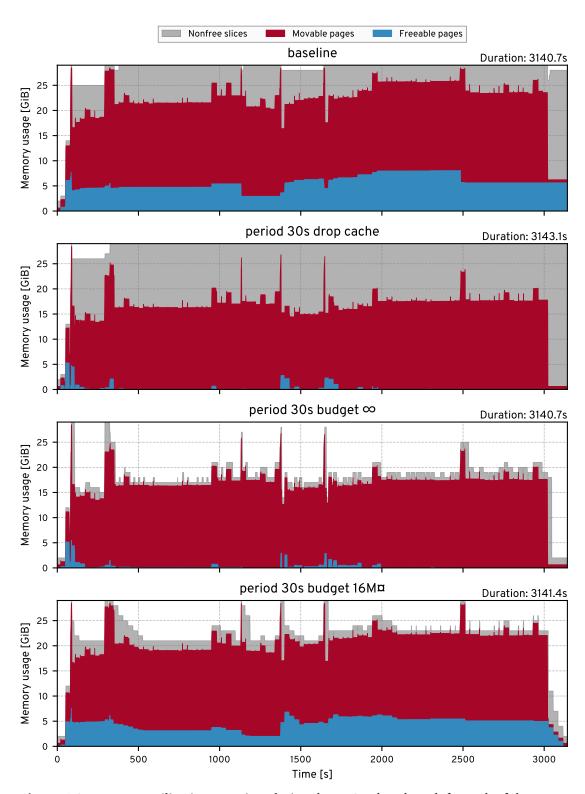

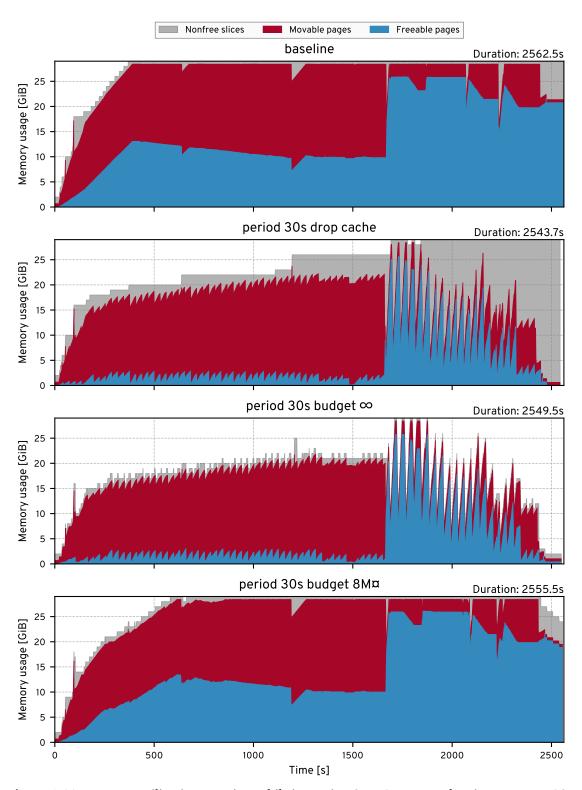

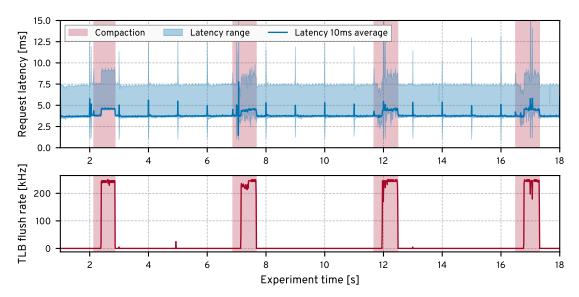

#### 3.2.1 Data Structures