# Performance Analysis of Single- and Multiprocessor Computing Systems

Dem Fachbereich Elektrotechnik und Informationstechnik der Universität Hannover

zur Erlangung des Grades

Dr.-Ing. habil.

vorgelegt von

Dr.-Ing. Jürgen Brehm

Hannover - 1999

# Contents

| 1.    | Introduction                                      | 1  |

|-------|---------------------------------------------------|----|

| 1.1.  | Basic Classification of Performance Analysis      | 1  |

| 1.2.  | Refined Classification of Performance Analysis    | 4  |

| 1.3.  | Organization of this Book                         | 6  |

| 2.    | Basic Notation and Definitions                    | 9  |

| 2.1.  | Notation                                          | 9  |

| 2.1.1 | . General Terms in the Context of this Work       | 9  |

| 2.1.2 | Program Task Graphs                               | 12 |

| 2.2.  | Performance Analysis Definitions                  | 13 |

| 2.2.1 | . Timing                                          | 13 |

| 2.2.2 | Performance Measures                              | 15 |

| 2.2.3 | Relative Performance Measures                     | 16 |

| 2.2.4 | System Under Test                                 | 21 |

| 2.2.5 | Evaluation Triangle                               | 22 |

| 3.    | Performance Analysis of Monoprocessors            | 23 |

| 3.1.  | Benchmarking                                      | 23 |

| 3.1.1 | . Synthetic Workloads                             | 23 |

| 3.1.2 | . Kernels                                         | 29 |

| 3.1.3 | Application Suites (SPEC)                         | 31 |

| 3.1.4 | . Comparison of Benchmark Results                 | 37 |

| 3.2.  | Modeling                                          | 38 |

| 3.2.1 | . Queueing Networks                               | 40 |

| 3.2.2 | Basic Birth-Death Models                          | 41 |

| 3.2.3 | Birth-Death Models with Infinite Number of States | 45 |

| 3.2.4 | Generalized Birth-Death Models                    | 49 |

| 3.3.  | Simulation                                        | 51 |

Contents

| 4. B    | Benchmarking of Multiprocessors           | 55  |

|---------|-------------------------------------------|-----|

| 4.1.    | Architecture of Multiprocessors           | 55  |

| 4.1.1.  | Shared Memory versus Message Passing      | 55  |

| 4.1.2.  | System Examples                           | 58  |

| 4.1.2.1 | nCUBE/2                                   | 58  |

| 4.1.2.2 | INTEL Paragon                             | 60  |

| 4.1.2.3 | Cray T3D                                  | 62  |

| 4.2.    | Workloads for Multiprocessors             | 64  |

| 4.2.1.  | Kernel and Application Benchmarks         |     |

| 4.2.1.1 | LINPACK                                   | 64  |

| 4.2.1.2 | NAS Parallel Benchmarks                   | 66  |

| 4.2.1.3 | PERFECT Club Benchmarks                   | 68  |

| 4.2.1.4 |                                           |     |

| 4.2.1.5 |                                           |     |

| 4.2.1.6 |                                           |     |

| 4.2.1.7 |                                           |     |

| 4.2.1.8 |                                           |     |

| 4.2.2.  | LOOP Programs                             |     |

| 4.2.2.3 |                                           |     |

| 4.2.2.4 |                                           |     |

| 4.2.2.5 |                                           |     |

| 4.3.    | Summary Benchmarking                      | 102 |

| 5. P    | Performance Modeling for Multiprocessors  | 103 |

| 5.1.    | Queueing Networks                         | 106 |

| 5.1.1.  | Queueing Network Example                  | 106 |

| 5.1.2.  | Extended Queueing Networks                | 121 |

| 5.1.3.  | Hierarchical Approach for Complex Systems |     |

| 5.1.4.  | Application Areas for Queueing Networks   |     |

| 5.2.    | Petri Net Models                          | 127 |

| 5.2.1.  | GSPN Example                              | 129 |

| 5.2.1.1 | Definitions                               | 129 |

| 5.2.1.2 | Example: Queueing Strategies              | 129 |

| 5.2.1.3 | €                                         |     |

| 5.2.2.  | DSPN Example                              | 135 |

| 5.2.3.  | Application Areas for Petri Nets          | 138 |

| 5.3.    | Quantitative Performance Evaluation       | 139 |

| 5.4.    | Summary Performance Modeling              | 152 |

| <b>6. A</b> 1    | nalytical Performance Modeling for Massively Parallel Systems | 155 |

|------------------|---------------------------------------------------------------|-----|

| 6.1.             | System Description                                            | 158 |

| 6.1.1.           | Communication Model                                           | 158 |

| 6.1.2.           | Computation Model                                             | 159 |

| 6.1.3.           | System Examples                                               | 160 |

| 6.2.             | Application Description                                       | 161 |

| 6.2.1.           | Programming Model                                             | 161 |

| 6.2.2.           | Workload Model                                                | 161 |

| 6.3.             | Application Examples                                          | 163 |

| 6.3.1.           | Matrix Multiplication                                         | 163 |

| 6.3.1.1          | PerPreT Application Description of MM                         | 163 |

| 6.3.1.2          | Variation of Problem Size                                     | 167 |

| 6.3.1.3          | Variation of Number of Processors                             | 168 |

| 6.3.1.4          | Validation of the PerPreT Formulae                            | 169 |

| 6.3.2.           | Conjugate Gradient Method                                     | 171 |

| 6.3.2.1          | PerPreT Application Description of CG                         | 171 |

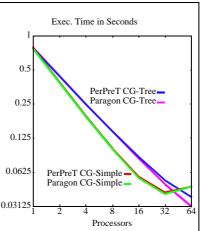

| 6.3.2.2          | Variation of Number of Processors                             | 173 |

| 6.3.2.3          | Variation of Problem Size                                     | 175 |

| 6.3.2.4          | Validation                                                    | 176 |

| 6.3.3.           | Shallow Water Code (PSTSWM)                                   | 178 |

| 6.3.3.1          | PerPreT Application Description of PSTSWM                     | 180 |

| 6.3.3.2          | Variation of Problem Size and Processors                      | 184 |

| 6.3.3.3          | Validation                                                    | 187 |

| 6.4.             | Summary PerPreT                                               | 193 |

| 7. TI            | ne PerPreT Software                                           | 195 |

| 7.1.             | Application Description                                       | 197 |

| 7.1.1.           | Computation Description (without phases)                      |     |

| 7.1.2.           | Computation Description (with phases)                         |     |

| 7.1.3.           | Communication Description                                     |     |

| 7.2.             | Application Examples                                          | 202 |

|                  | System Description                                            |     |

| 7.3.1.           | Computation Description (without phases)                      |     |

| 7.3.2.           | Computation Description (with phases)                         |     |

| 7.3.3.           | Communication Description                                     |     |

|                  | Experiments                                                   |     |

| 7.4.1.           | •                                                             |     |

| 7.4.1.<br>7.4.2. | Experiments with Varying Processor Number                     |     |

|                  | Experiments with Varying Problem Size                         |     |

|                  | Validation                                                    |     |

| 7.5.1.           | Compare Model and Experimental Data                           | 214 |

| 7.6. Summary PerPreT Software                        | 218 |

|------------------------------------------------------|-----|

| 8. Open Problems in Performance Analysis .           | 219 |

| 8.1. Parallel Applications with Irregular Topologies | 219 |

| 8.2. Workstation Clusters                            | 220 |

| 8.3. Performance Analysis of Software                | 220 |

| 8.4. Embedded Control Systems                        | 221 |

| 8.5. Summary Open Problems                           | 221 |

# **List of Figures**

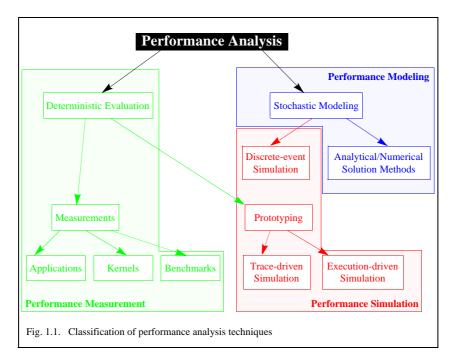

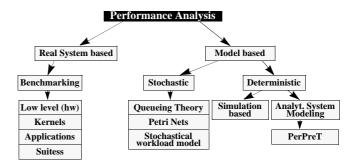

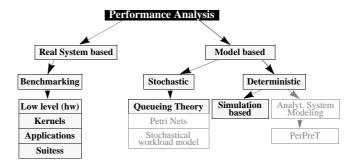

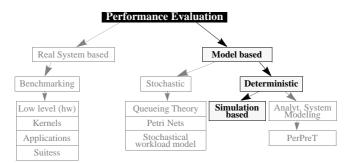

| Fig. 1.1.  | Classification of performance analysis techniques                         | 2     |

|------------|---------------------------------------------------------------------------|-------|

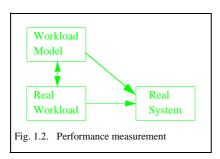

| Fig. 1.2.  | Performance measurement                                                   | 3     |

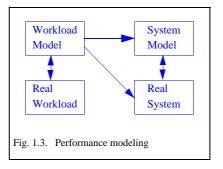

| Fig. 1.3.  | Performance modeling                                                      | 3     |

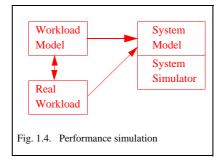

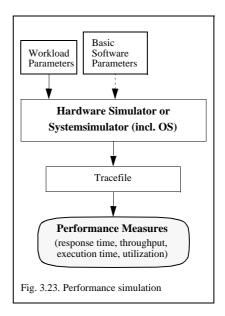

| Fig. 1.4.  | Performance simulation                                                    | 3     |

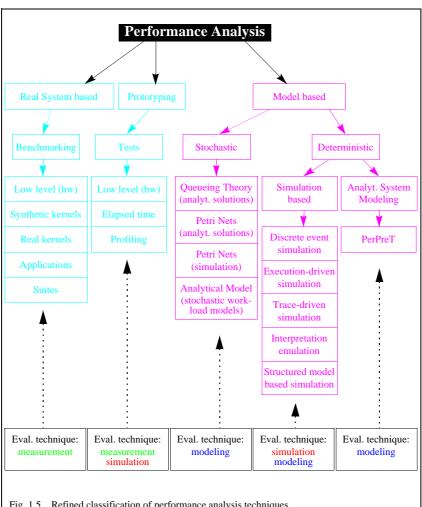

| Fig. 1.5.  | Refined classification of performance analysis techniques                 | 5     |

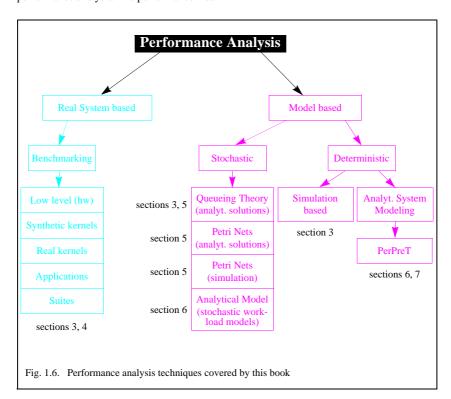

| Fig. 1.6.  | Performance analysis techniques covered by this book                      | 6     |

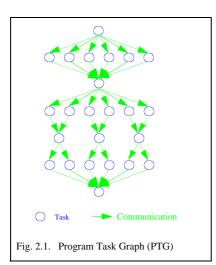

| Fig. 2.1.  | Program Task Graph (PTG)                                                  |       |

| Fig. 2.2.  | Mapping of a parallel workload described by a PTG onto 6 processors       | 12    |

| Fig. 2.3.  | Possible process states during the execution of a parallel program        | 13    |

| Fig. 2.4.  | Parallel program execution                                                | 13    |

| Fig. 2.5.  | Basic system model                                                        | 15    |

| Fig. 2.6.  | Speedup functions for various seq using Amdahl's law.                     | 17    |

| Fig. 2.7.  | Efficiency functions for various numbers of processors P                  |       |

| Fig. 2.8.  | Speedup (Amdahl) and scaled speedup (Gustafson)                           | 19    |

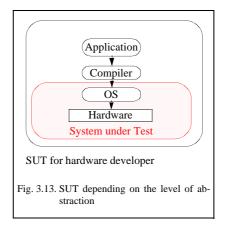

| Fig. 2.9.  | SUT depending on the level of abstraction                                 | 21    |

| Fig. 2.10. | Evaluation triangle                                                       | 22    |

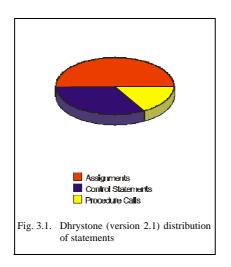

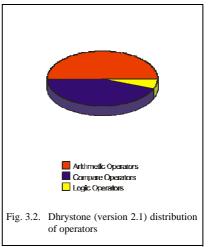

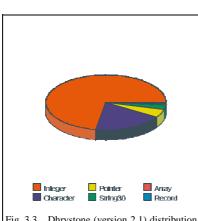

| Fig. 3.1.  | Dhrystone (version 2.1) distribution of statements                        |       |

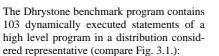

| Fig. 3.2.  | Dhrystone (version 2.1) distribution of operators                         | 24    |

| Fig. 3.3.  | Dhrystone (version 2.1) distribution of operands with respect to types    | 25    |

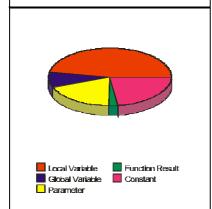

| Fig. 3.4.  | Dhrystone (version 2.1) distribution of operands with respect to locality | 25    |

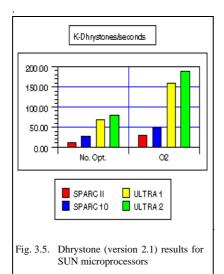

| Fig. 3.5.  | Dhrystone (version 2.1) results for SUN microprocessors                   | 26    |

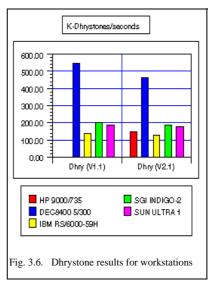

| Fig. 3.6.  | Dhrystone results for workstations                                        | 26    |

| Fig. 3.7.  | Whetstone results for SUN microprocessors                                 |       |

| Fig. 3.8.  | Linpack results                                                           | 30    |

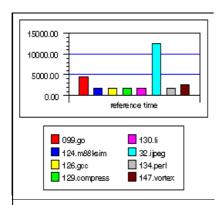

| Fig. 3.9.  | SPEC CINT95 (integer) benchmarks (reference times in seconds)             | 33    |

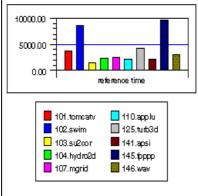

| Fig. 3.10. | ` I '                                                                     |       |

| Fig. 3.11. | SPECfp95 and SPECint95 results                                            | 34    |

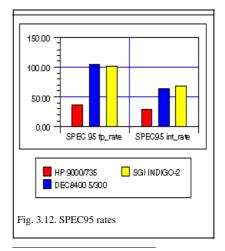

| Fig. 3.12. | SPEC95 rates                                                              | 35    |

|            | SUT depending on the level of abstraction                                 |       |

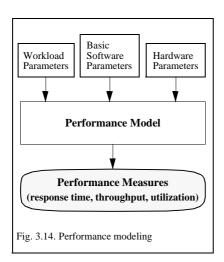

| Fig. 3.14. | Performance modeling                                                      | 39    |

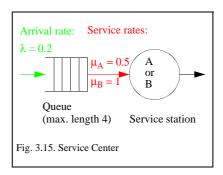

| Fig. 3.15. | Service Center                                                            | 40    |

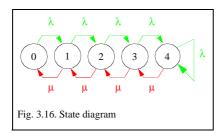

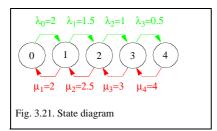

|            | State diagram                                                             |       |

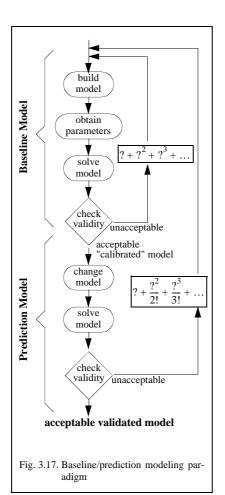

|            | Baseline/prediction modeling paradigm                                     |       |

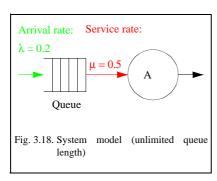

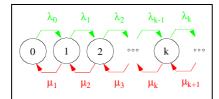

|            | System model (unlimited queue length)                                     |       |

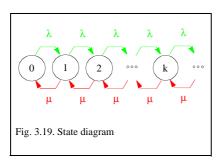

|            | State diagram                                                             |       |

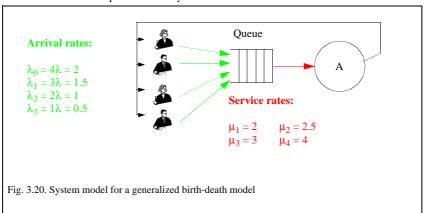

| Fig. 3.20. | System model for a generalized birth-death model                          | 48    |

| U          | State diagram                                                             |       |

|            | Generalized birth death state-space diagram                               |       |

|            | Performance simulation                                                    |       |

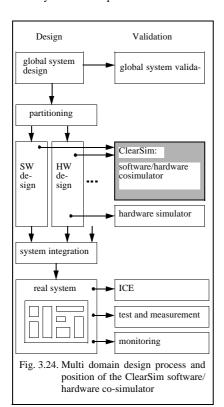

| Fig. 3.24. | Multi domain design process and position of the ClearSim software/hardwar | e co- |

|            | simulator                                                                 | 53    |

List of Figures

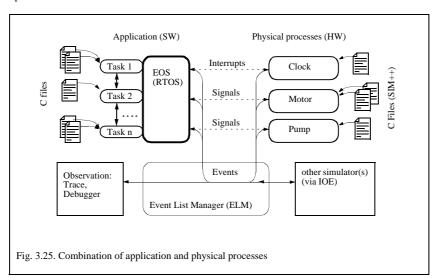

| Fig. 3.25. | Combination of application and physical processes                   | 54   |

|------------|---------------------------------------------------------------------|------|

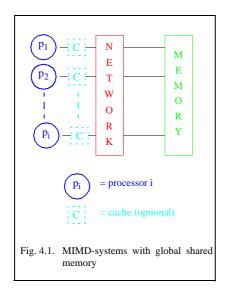

| Fig. 4.1.  | MIMD-systems with global shared memory                              |      |

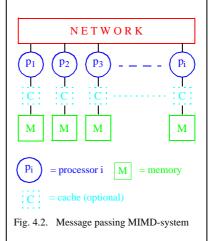

| Fig. 4.2.  | Message passing MIMD-system                                         | 56   |

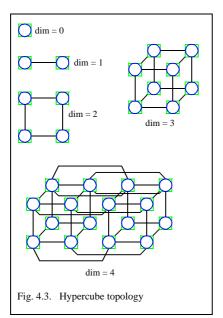

| Fig. 4.3.  | Hypercube topology                                                  | 58   |

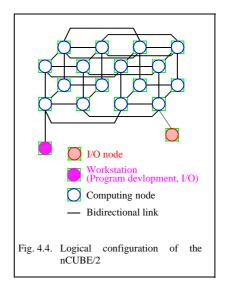

| Fig. 4.4.  | Logical configuration of the nCUBE/2                                | 59   |

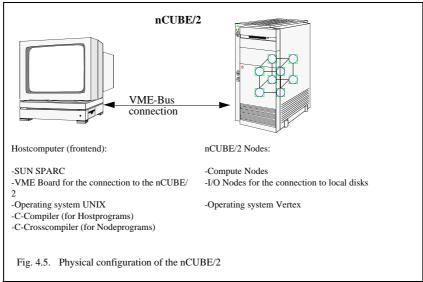

| Fig. 4.5.  | Physical configuration of the nCUBE/2                               | 59   |

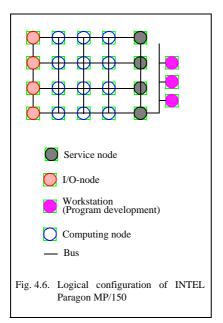

| Fig. 4.6.  | Logical configuration of INTEL Paragon MP/150                       | 60   |

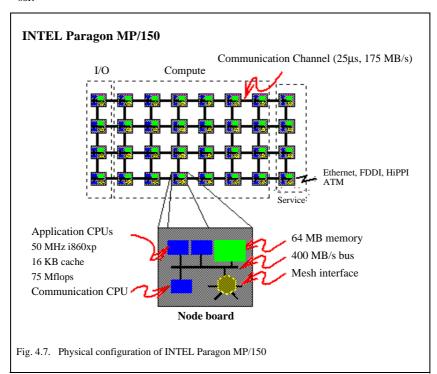

| Fig. 4.7.  | Physical configuration of INTEL Paragon MP/150                      | 61   |

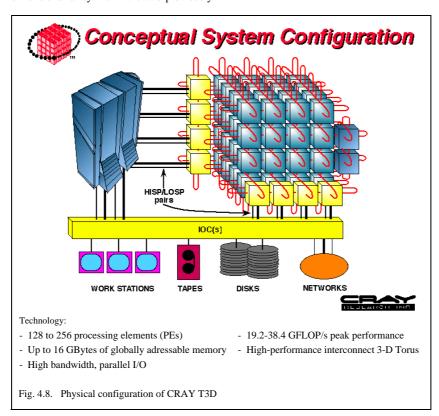

| Fig. 4.8.  | Physical configuration of CRAY T3D                                  | 62   |

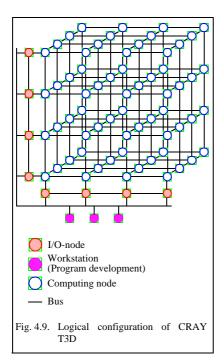

| Fig. 4.9.  | Logical configuration of CRAY T3D                                   | 63   |

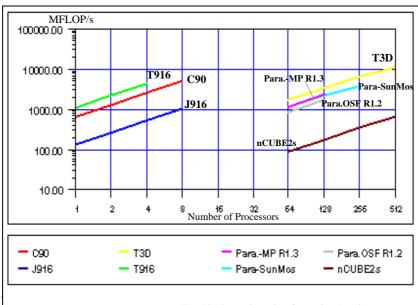

| Fig. 4.10. | Results from PARKBENCH's Graphical Benchmark Information Service    | 75   |

| Fig. 4.11. | The SPEC High-Performance Group                                     | 83   |

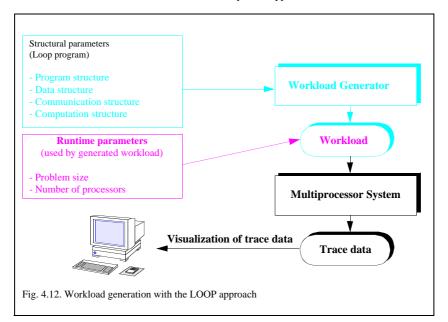

| Fig. 4.12. | Workload generation with the LOOP approach                          | 86   |

| Fig. 4.13. | Complete LOOP program for a parallel matrix multiplication          | 88   |

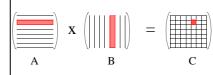

| Fig. 4.14. | Structure of a parallel matrix multiplication                       | 89   |

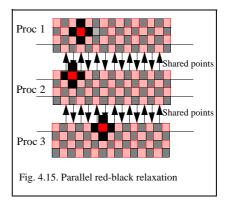

|            | Parallel red-black relaxation                                       |      |

| Fig. 4.16. | LOOP program for parallel red-black relaxation                      | 91   |

| Fig. 4.17. | LOOP source code for Fingerprint                                    | 94   |

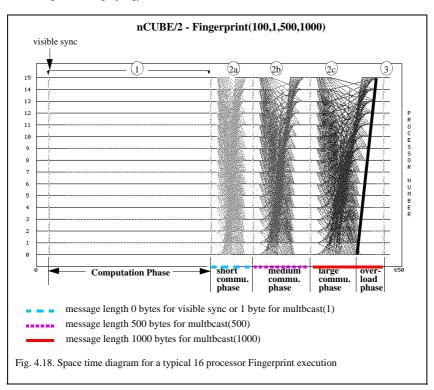

|            | Space time diagram for a typical 16 processor Fingerprint execution |      |

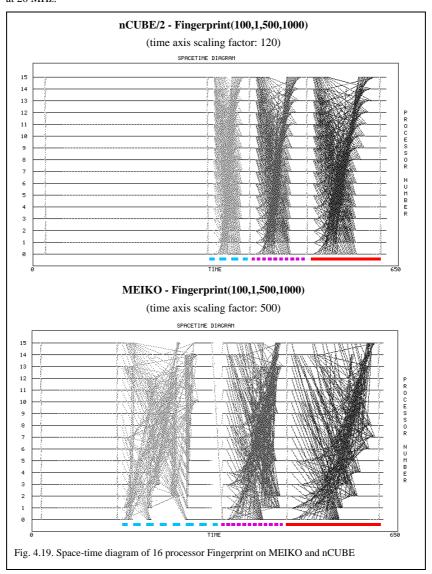

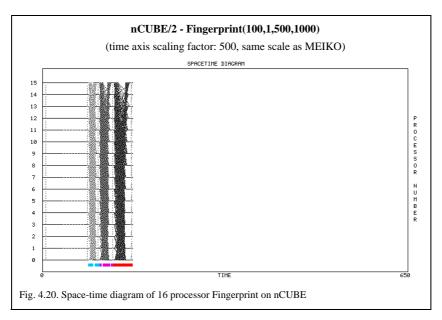

| Fig. 4.19. | Space-time diagram of 16 processor Fingerprint on MEIKO and nCUBE   | 96   |

| Fig. 4.20. | Space-time diagram of 16 processor Fingerprint on nCUBE             | 97   |

| Fig. 4.21. | Deterministic performance evaluation                                | .102 |

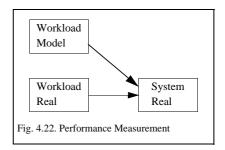

| Fig. 4.22. | Performance Measurement                                             | .102 |

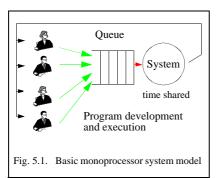

| Fig. 5.1.  | Basic monoprocessor system model                                    | .104 |

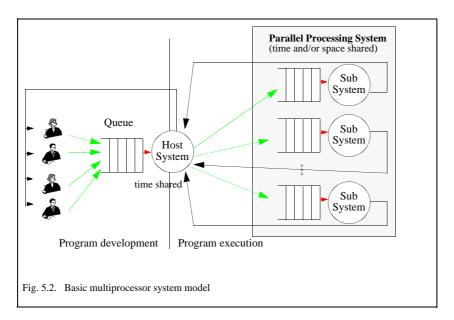

| Fig. 5.2.  | Basic multiprocessor system model                                   | .105 |

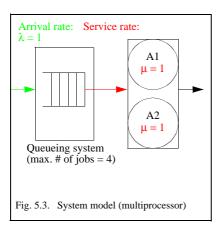

| Fig. 5.3.  | System model (multiprocessor)                                       | .106 |

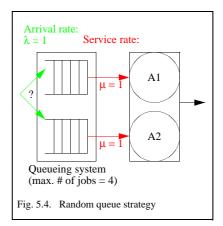

| Fig. 5.4.  | Random queue strategy                                               | .106 |

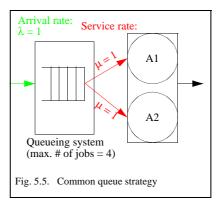

| Fig. 5.5.  | Common queue strategy                                               | .106 |

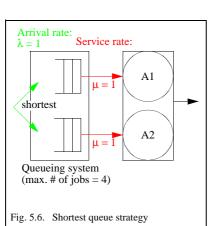

| Fig. 5.6.  | Shortest queue strategy                                             | .107 |

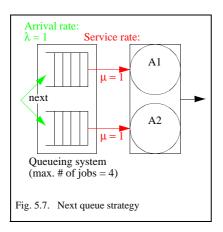

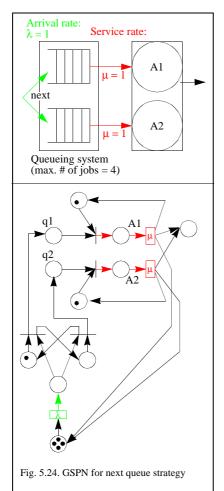

| Fig. 5.7.  | Next queue strategy                                                 | .107 |

| Fig. 5.8.  | State diagram of random queue                                       | .108 |

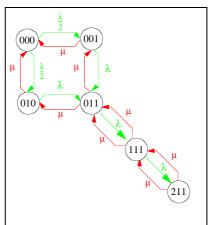

| Fig. 5.9.  | State diagram of common queue                                       | .111 |

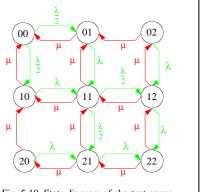

| Fig. 5.10. | State diagram of shortest queue                                     | .113 |

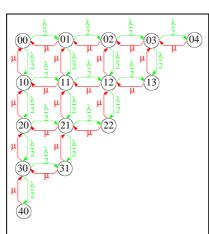

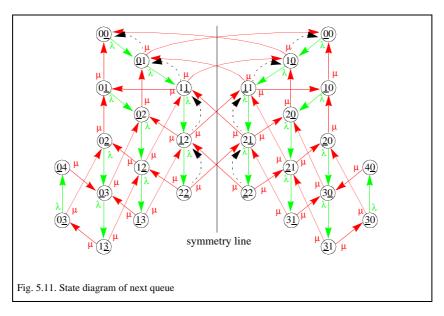

| Fig. 5.11. | State diagram of next queue                                         | .116 |

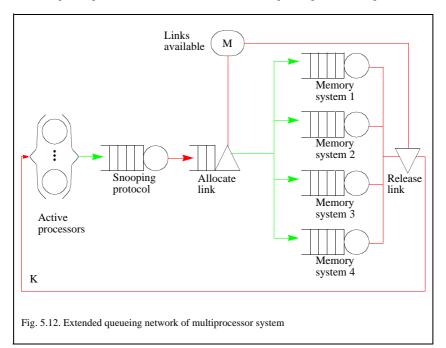

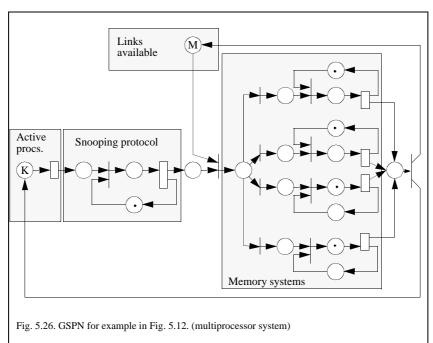

| Fig. 5.12. | Extended queueing network of multiprocessor system                  | .121 |

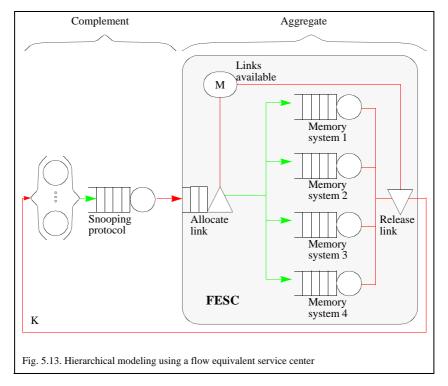

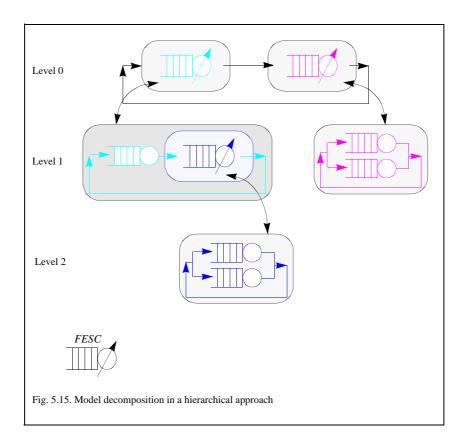

| Fig. 5.13. | Hierarchical modeling using a flow equivalent service center        | .123 |

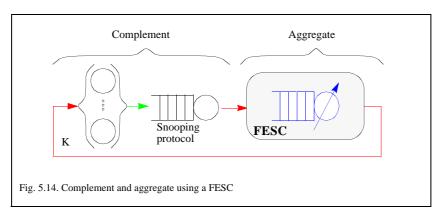

|            | Complement and aggregate using a FESC                               |      |

| Fig. 5.15. | Model decomposition in a hierarchical approach                      | .125 |

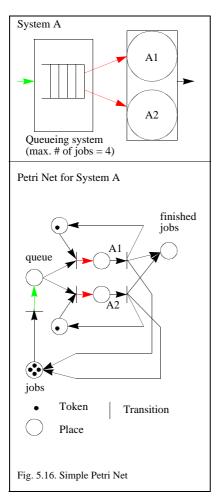

| Fig. 5.16. | Simple Petri Net                                                    | .127 |

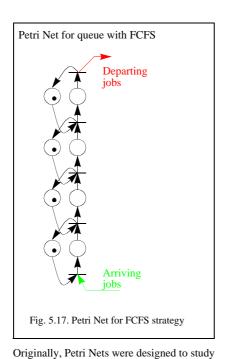

|            | Petri Net for FCFS strategy                                         |      |

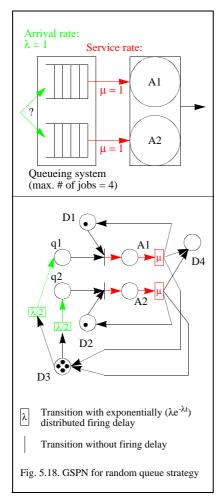

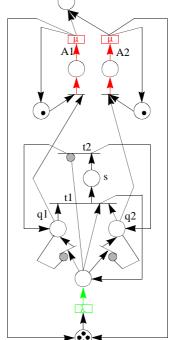

| Fig. 5.18. | GSPN for random queue strategy                                      | .130 |

| Fig. 5.19. | Generation of reachability set                                      | .130 |

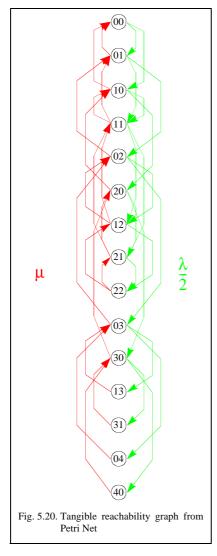

| Fig. 5.20. | Tangible reachability graph from Petri Net                          | .131 |

List of Figures vii

| F: 5.01    | CODY                                                                      | 101 |

|------------|---------------------------------------------------------------------------|-----|

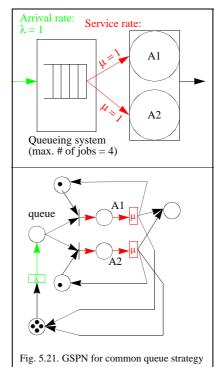

|            | GSPN for common queue strategy                                            |     |

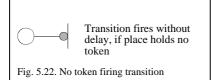

| _          | No token firing transition                                                |     |

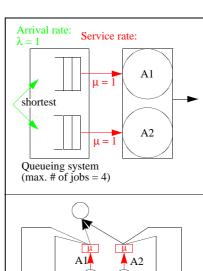

| -          | GSPN for shortest queue strategy                                          |     |

|            | GSPN for next queue strategy                                              |     |

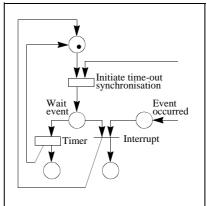

| _          | GSPN for a time-out synchronization                                       |     |

|            | GSPN for example in Fig. 5.12. (multiprocessor system)                    |     |

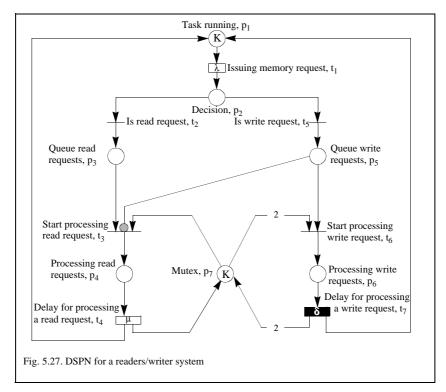

|            | DSPN for a readers/writer system                                          |     |

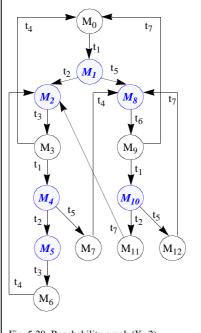

|            | Generation of reachability set (K=2)                                      |     |

|            | Reachability graph (K=2)                                                  |     |

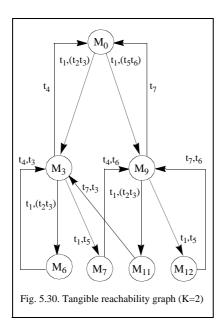

|            | Tangible reachability graph (K=2)                                         |     |

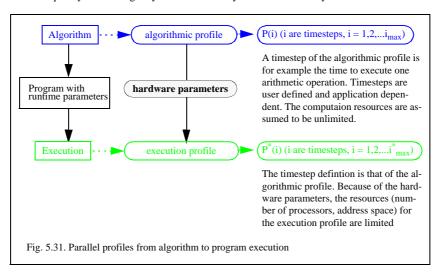

| Fig. 5.31. | Parallel profiles from algorithm to program execution                     | 140 |

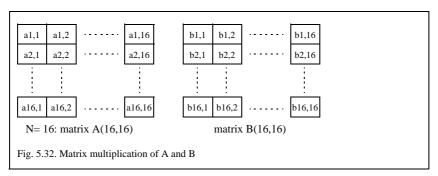

|            | Matrix multiplication of A and B                                          |     |

|            | Algorithmic profile for parallel matrix multiply with $N=16$              |     |

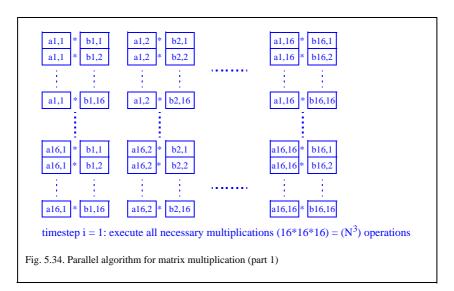

|            | Parallel algorithm for matrix multiplication (part 1)                     |     |

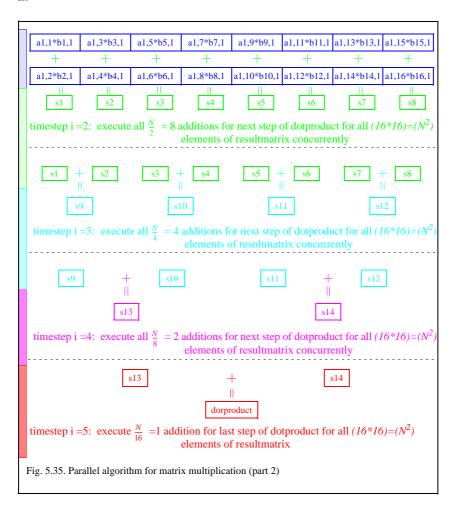

| Fig. 5.35. | Parallel algorithm for matrix multiplication (part 2)                     | 142 |

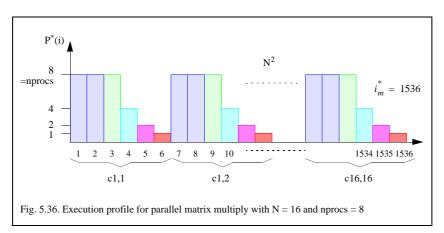

| Fig. 5.36. | Execution profile for parallel matrix multiply with $N=16$ and $nprocs=8$ | 143 |

| Fig. 5.37. | Execution profile for matrix multiply with nprocs = 1                     | 144 |

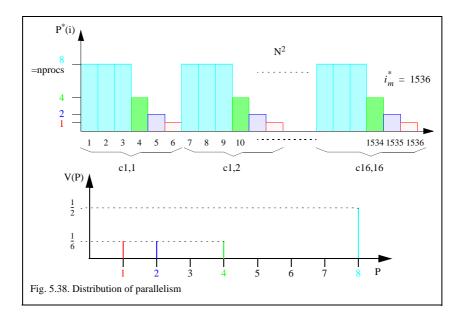

| Fig. 5.38. | Distribution of parallelism                                               | 145 |

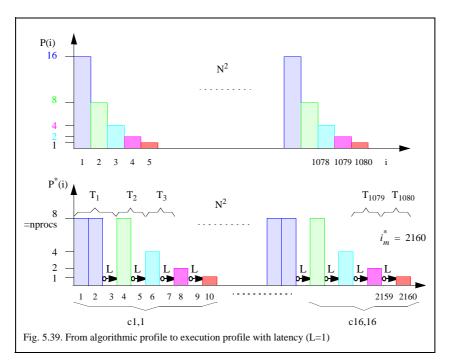

| Fig. 5.39. | From algorithmic profile to execution profile with latency (L=1)          | 146 |

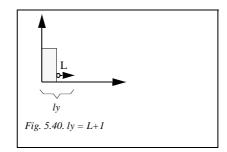

| Fig. 5.40. | ly = L+1                                                                  | 147 |

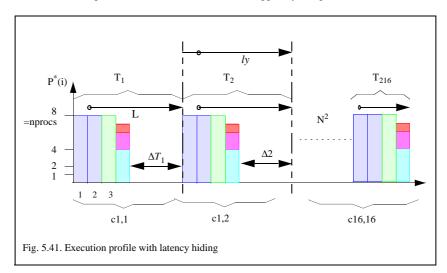

| Fig. 5.41. | Execution profile with latency hiding                                     | 148 |

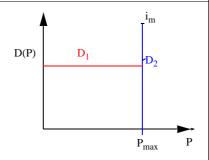

| Fig. 5.42. | Distribution functions D1 and D2                                          | 149 |

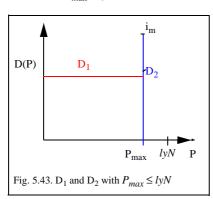

| Fig. 5.43. | D1 and D2 with Pmax £ lyN                                                 | 150 |

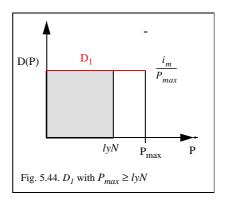

| Fig. 5.44. | D1 with Pmax Š lyN                                                        | 150 |

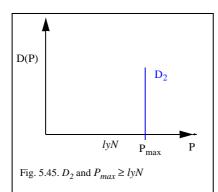

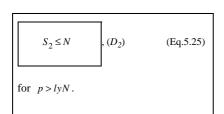

| Fig. 5.45. | D2 and Pmax Š lyN                                                         | 151 |

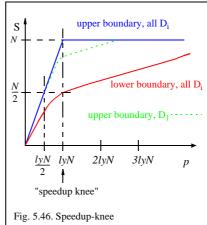

| Fig. 5.46. | Speedup-knee                                                              | 151 |

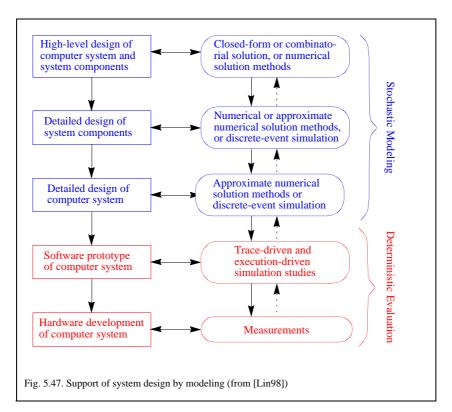

| Fig. 5.47. | Support of system design by modeling (from [Lin98])                       | 153 |

| Fig. 5.48. | The modeling cycle                                                        | 154 |

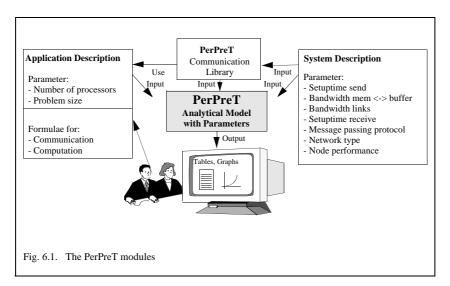

| Fig. 6.1.  | The PerPreT modules                                                       |     |

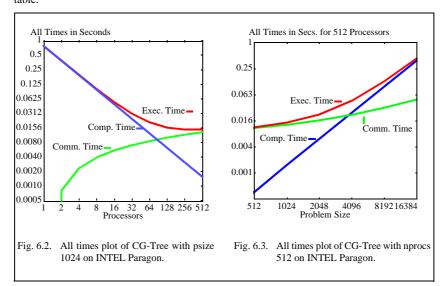

| Fig. 6.2.  | All times plot of CG-Tree with psize 1024 on INTEL Paragon                | 157 |

| Fig. 6.3.  | All times plot of CG-Tree with nprocs 512 on INTEL Paragon                |     |

| Fig. 6.4.  | Die PerPreT Module                                                        | 157 |

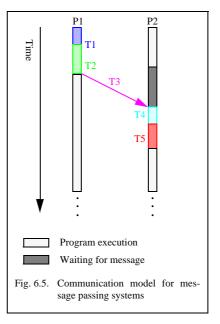

| Fig. 6.5.  | Communication model for message passing systems                           | 158 |

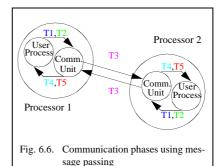

| Fig. 6.6.  | Communication phases using message passing                                |     |

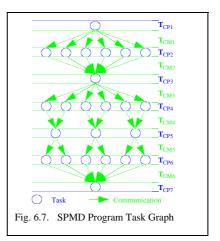

| Fig. 6.7.  | SPMD Program Task Graph                                                   |     |

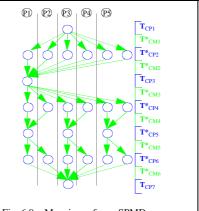

| Fig. 6.8.  | Mapping of an SPMD program onto 6 processors                              |     |

| Fig. 6.9.  | Mapping of an SPMD program onto 5 processors                              |     |

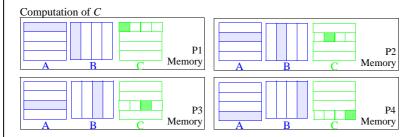

| _          | Version 1 of parallel matrix multiplication                               |     |

| _          | Version 2 of parallel matrix multiplication                               |     |

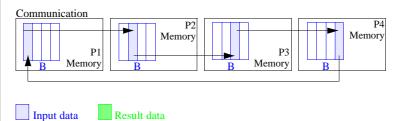

|            | Version 2 of parallel matrix multiplication (steps 2 to nprocs-1)         |     |

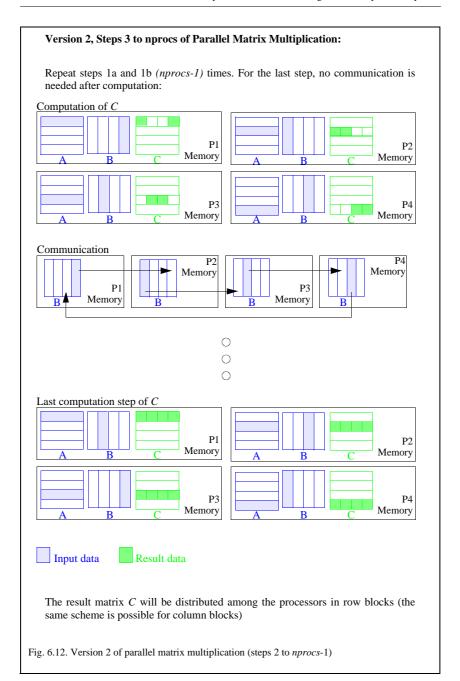

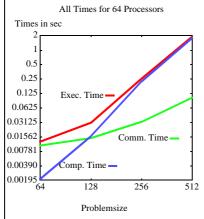

|            | Predicted time for Version 2 of parallel MM on INTEL Paragon              |     |

| 8. 0.10.   | with varying psize                                                        | 167 |

| Fig. 6.14. | Predicted time for Version 2 of parallel MM on INTEL Paragon              |     |

viii List of Figures

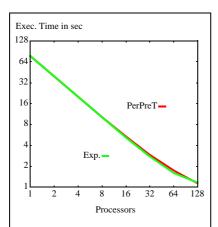

| Fig. 6.15. | Comparison of actual and predicted execution times of parallel MM for psize = 256 on nCUBE/2 | 170  |

|------------|----------------------------------------------------------------------------------------------|------|

| Fig. 6.16. | Comparison of actual and predicted execution times of parallel MM                            |      |

| -          | for psize = 256 on INTEL Paragon                                                             |      |

| Fig. 6.17. | PTG for parallel CG Method                                                                   | 171  |

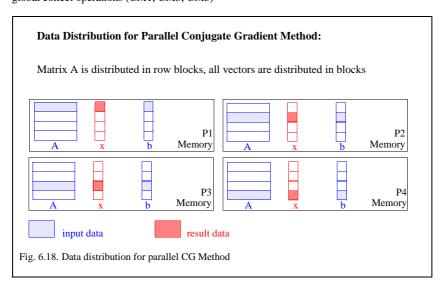

|            | Data distribution for parallel CG Method                                                     |      |

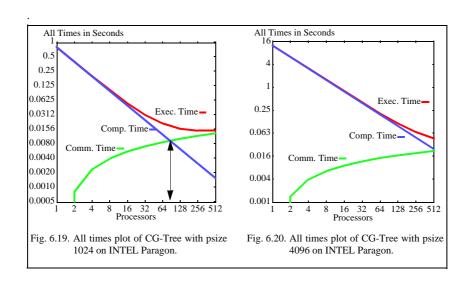

| Fig. 6.19. | All times plot of CG-Tree with psize 1024 on INTEL Paragon                                   | 175  |

| Fig. 6.20. | All times plot of CG-Tree with psize 4096 on INTEL Paragon                                   | 175  |

| Fig. 6.21. | All times plot of CG-Tree (512 processors, varying psize) on INTEL Paragon                   | 175  |

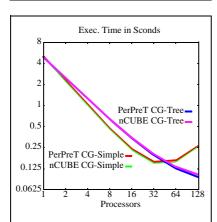

| Fig. 6.22. | Comparison of actual and predicted execution times of CG-Methods for                         |      |

|            | psize = 1024 on an nCUBE/2                                                                   | 177  |

| Fig. 6.23. | Comparison of actual and predicted execution times of CG-Methods for                         | 1.55 |

| E: < 0.4   | psize = 512 on an INTEL Paragon                                                              |      |

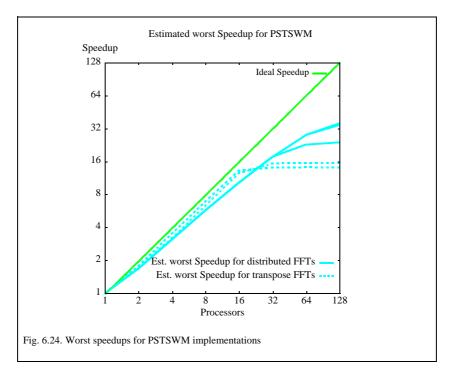

| Fig. 6.24. | Worst speedups for PSTSWM implementations                                                    |      |

| _          | Performance modeling                                                                         |      |

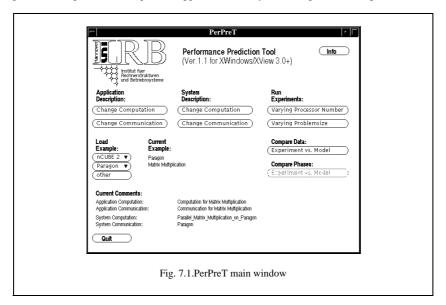

| Fig. 7.1.  | PerPreT main window                                                                          |      |

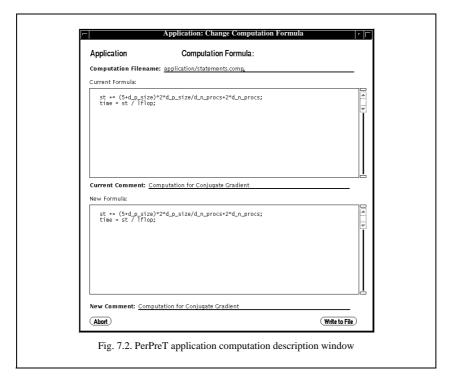

| Fig. 7.2.  | PerPreT application computation description window                                           |      |

| Fig. 7.3.  | Extract of PSTSWM computation description                                                    |      |

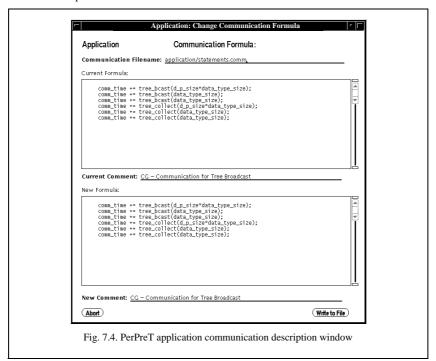

| Fig. 7.4.  | PerPreT application communication description window                                         |      |

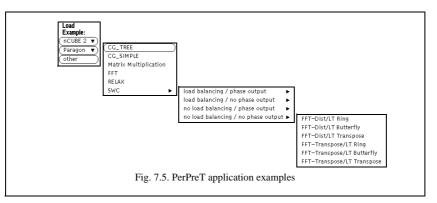

| Fig. 7.5.  | PerPreT application examples                                                                 |      |

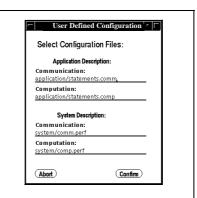

| Fig. 7.6.  | Load user defined examples                                                                   |      |

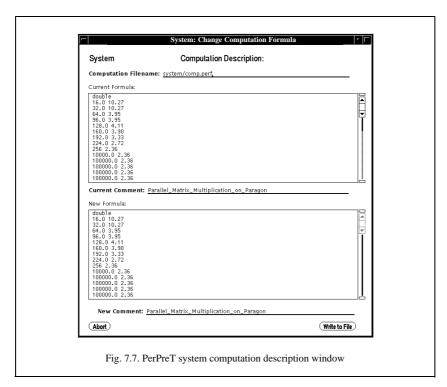

| Fig. 7.7.  | PerPreT system computation description window                                                |      |

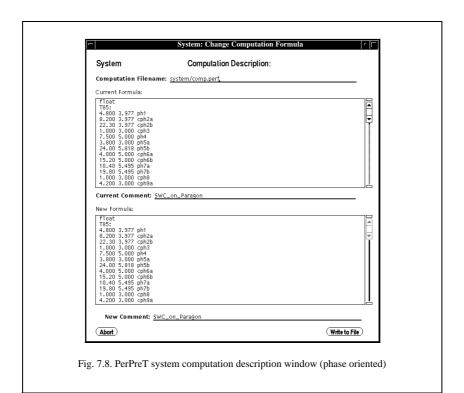

| Fig. 7.8.  | PerPreT system computation description window (phase oriented)                               |      |

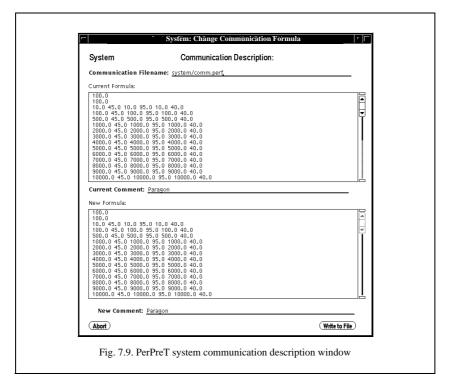

| Fig. 7.9.  | PerPreT system communication description window                                              | 206  |

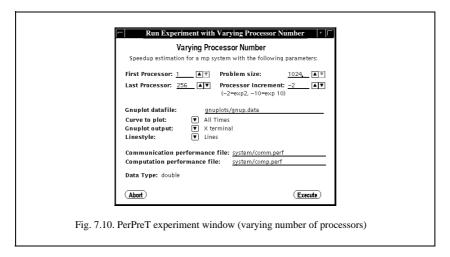

| Fig. 7.10. | PerPreT experiment window (varying number of processors)                                     | 207  |

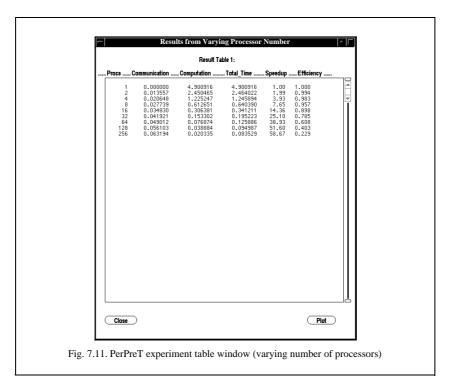

| Fig. 7.11. | PerPreT experiment table window (varying number of processors)                               | 208  |

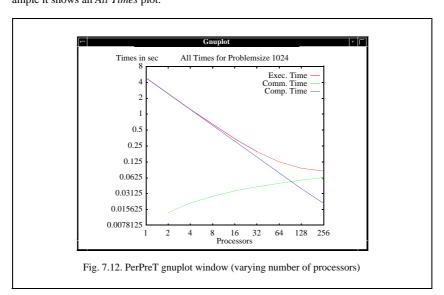

| Fig. 7.12. | PerPreT gnuplot window (varying number of processors)                                        | 209  |

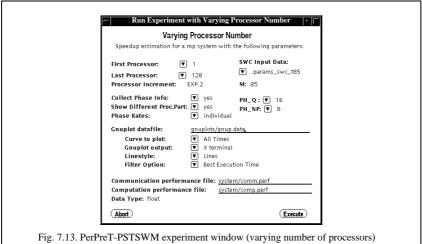

| Fig. 7.13. | PerPreT-PSTSWM experiment window (varying number of processors)                              | 210  |

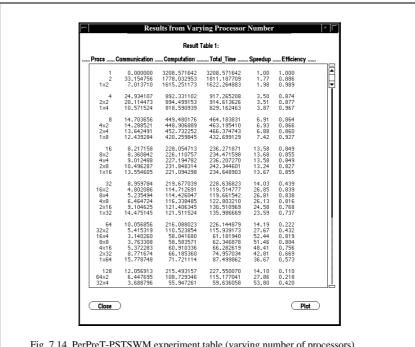

| Fig. 7.14. | PerPreT-PSTSWM experiment table (varying number of processors)                               | 210  |

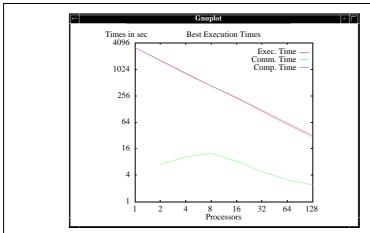

| Fig. 7.15. | PerPreT-PSTSWM gnuplot window (varying number of processors)                                 | 211  |

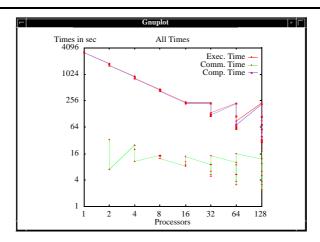

| Fig. 7.16. | PerPreT-PSTSWM gnuplot window (varying number of processors)                                 | 211  |

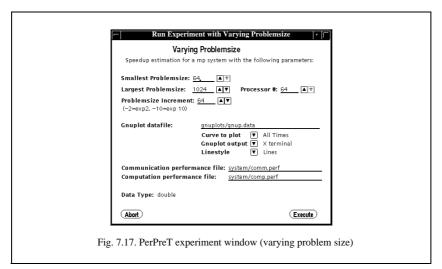

| Fig. 7.17. | PerPreT experiment window (varying problem size)                                             | 212  |

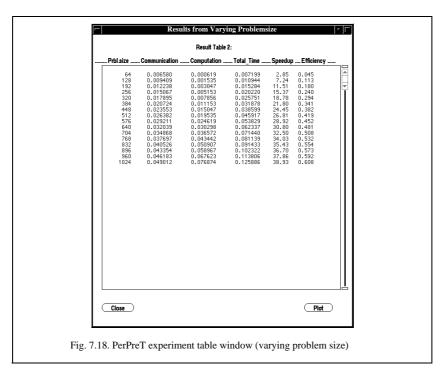

| Fig. 7.18. | PerPreT experiment table window (varying problem size)                                       | 213  |

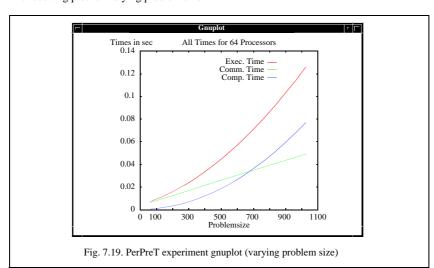

| Fig. 7.19. | PerPreT experiment gnuplot (varying problem size)                                            | 213  |

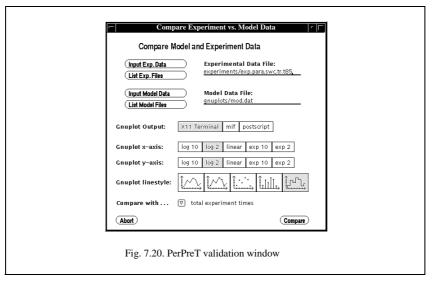

|            | PerPreT validation window                                                                    |      |

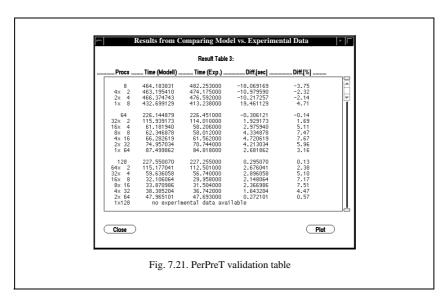

|            | PerPreT validation table                                                                     |      |

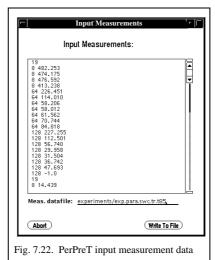

| _          | PerPreT input measurement data                                                               |      |

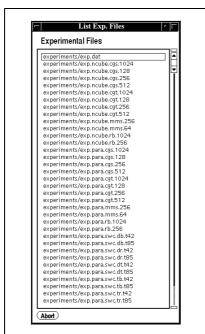

| -          | PerPreT experimental data file selection                                                     |      |

|            | PerPreT model data file selection                                                            |      |

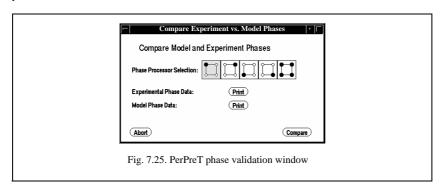

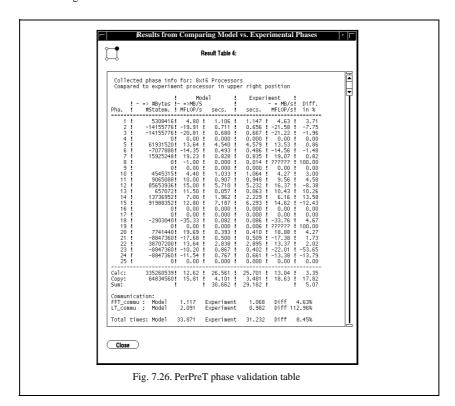

| _          | PerPreT phase validation window                                                              |      |

| -          | PerPreT phase validation table                                                               |      |

| _          | PerPreT contact information                                                                  |      |

# **List of Tables**

| Tab. 2.1.  | SPEC CPU benchmarks (Release 1)                                                     | 20  |

|------------|-------------------------------------------------------------------------------------|-----|

| Tab. 3.1.  | Dhrystone results for workstations                                                  | 27  |

| Tab. 3.2.  | Linpack results for workstations                                                    | 29  |

| Tab. 3.3.  | SPEC CINT95 (integer) benchmarks                                                    | 31  |

| Tab. 3.4.  | SPEC CFP95 (floating point) benchmarks                                              | 32  |

| Tab. 3.5.  | SPEC 95 results published by SPEC                                                   | 34  |

| Tab. 3.6.  | SPEC 95 rates published by SPEC                                                     | 35  |

| Tab. 3.7.  | Comparison of benchmark results for workstations                                    | 37  |

| Tab. 3.8.  | Comparison of systems A and B                                                       |     |

| Tab. 3.9.  | Comparison of systems A and B with new arrival rates                                | 43  |

| Tab. 4.10. | Linpack results for massively parallel machines                                     | 65  |

|            | NAS Parallel Benchmarks problem sizes                                               |     |

| Tab. 4.12. | NAS Parallel Benchmarks results for one node of CRAY Y-MP                           | 67  |

| Tab. 4.13. | PERFECT Benchmark baseline results (in MFLOP/s)                                     | 71  |

| Tab. 4.14. | PERFECT Benchmark optimized results (in MFLOP/s)                                    | 72  |

| Tab. 4.15. | Characteristics of SPLASH-2 applications and kernels                                | 78  |

| Tab. 4.16. | SLALOM benchmark results for single processor SGI 4D/380S                           | 80  |

| Tab. 4.17. | SLALOM benchmarks results                                                           | 81  |

| Tab. 4.18. | Comparison of MEIKO and nCUBE using a 16 processor Fingerprint                      | 98  |

| Tab. 4.19. | Comparison of MEIKO and nCUBE using a 32 processor Fingerprint                      | 98  |

| Tab. 4.20. | Execution times for the LOOP benchmarks                                             | 99  |

| Tab. 4.21. | Slowdown against Paragon                                                            | 100 |

| Tab. 5.1.  | State probabilities for random queue                                                | 109 |

| Tab. 5.2.  | Results for common queue                                                            | 112 |

| Tab. 5.3.  | Results for shortest queue                                                          | 114 |

| Tab. 5.4.  | Results for next queue                                                              | 119 |

| Tab. 5.5.  | Comparison of the four queueing strategies (absolute values)                        |     |

| Tab. 5.6.  | Comparison of the four queueing strategies (relative values)                        |     |

| Tab. 5.7.  | Loss of parallelism caused by problem formulation                                   |     |

| Tab. 6.1.  | PerPreT result table for parallel MM on INTEL Paragon (varying psize)               |     |

| Tab. 6.2.  | $PerPreT\ result\ table\ for\ parallel\ MM\ on\ INTEL\ Paragon\ (varying\ nprocs)\$ | 169 |

| Tab. 6.3.  | Validation of parallel MM using 1 to 128 processors on nCUBE/2                      |     |

| Tab. 6.4.  | Validation of parallel MM using 1 to 64 processors on INTEL Paragon                 |     |

| Tab. 6.5.  | PerPreT result table for modeling a parallel CG Method on Paragon                   |     |

| Tab. 6.6.  | Output Table for CG-Tree (varying psize, 512 processors) on Paragon                 |     |

| Tab. 6.7.  | Validation of parallel CG-Simple on nCUBE/2 (psize = 1024)                          |     |

| Tab. 6.8.  | Validation of parallel CG-Tree on nCUBE/2 (psize = 1024)                            |     |

| Tab. 6.9.  | $Validation\ of\ parallel\ CG-Simple\ on\ INTEL\ Paragon\ (psize=1024)\$            |     |

| Tab. 6.10. | Validation of parallel CG-Tree on INTEL Paragon (psize = 1024)                      | 177 |

| Tab 6.11   | Candidate PSTSWM parallel algorithms                                                | 180 |

List of Tables

| Tab. 6.12. | Computational models and MFLOP/s or MByte/s rates for algorithm TH            | 182 |

|------------|-------------------------------------------------------------------------------|-----|

| Tab. 6.13. | Communication models for forward and inverse transforms                       | 183 |

| Tab. 6.14. | PerPreT result table for modeling PSTSWM on Paragon                           | 185 |

| Tab. 6.15. | Problem size parameters for PSTSWM                                            | 187 |

| Tab. 6.16. | Error in choosing optimal ratio from model results                            | 188 |

| Tab. 6.17. | Validation of PSTSWM (TR-T85) using 8 processors                              | 188 |

| Tab. 6.18. | Validation of PSTSWM (TR-T85) using 64 processors                             | 188 |

| Tab. 6.19. | Validation of PSTSWM (TR-T85) using 128 processors                            | 188 |

| Tab. 6.20. | Error in choosing optimal alg. from model results instead of experimentally . | 189 |

| Tab. 6.21. | Error in predicting runtimes (seconds)                                        | 190 |

| Tab. 6.22. | Error in choosing optimal algorithm from complexity                           |     |

|            | analysis instead of experimentally                                            | 191 |

| Tab. 6.23. | Error in predicting runtime (seconds) using complexity based model            | 191 |

| Tab. 6.24. | Error in predicting runtime (seconds) using single phase model                | 192 |

## **Abbreviations**

- ALU Arithmetic - logic unit

- BLAS

Basic Linear Algebra Subprograms

- CFD

Computational Fluid Dynamics

- CG

Conjugate Gradient

- CMi

Communication phase i

---

CPi Computation phase i

- CPU

Central Processing Unit

- DEC

Digital Equipment Corporation

- DMA

Direct Memory Access

- d\_n\_procs

PerPreT variable for number of processors

- d\_p\_size

PerPreT variable for problem size

- DSPN

Deterministic and Stochastic Petri Net

- FCFS

First Come First Serve

- FESC

Flow Equivalent Service Center

- FFT

Fast Fourier Transform

- GAMESS

General Atomic and Molecular Electronic

Structure System

- GBIS

Graphical Benchmark Information Service

- GSPN

Generalized Stochastic Petri Net

- HP

Hewlett Packard

- HPG

High Performance Group

- HPF

High Performance Fortran

- IS

Integer Sort

- λ

Arrival rate

- LAN

Local Area Network

- lflop

PerPreT variable for node performance

- I.T

Legendre Transform

- μ

Departure rate

- mflop[][]

PerPreT variable for node performance

- MFLOPS

Mega Floating Point Operations per Sec-

ond - MG

Multigrid

- MIMD

Multiple Instruction Multiple Data

- MM

Matrix Multiplication

MIDC

Millions of Instructions per Second

MDI

Message Passing Interface

- MVA

Mean Value Analysis

- N

Problem size

xii Abbreviations

- NAS

Numerical Aerodynamic Simulation

- NPB

NAS Parallel Benchmarks

- nprocs

Number of processors

- psize

Problem size

Number of processors

- PARKBENCH

PARallel Kernels and BENCHmarks

Performance Evaluation for Cost-effective Transformations

- PerPreT

Performance Prediction Tool

Portable Instrumented Communication Library

- PIP

Parallel Instrumented Program

Parallel Spectral Transform Shallow Water Model

- PTG

Program Task Graph

- PVM

Parallel Virtual Machine

- SIMD

Single Instruction Multiple Data

Scalable, Language-independent, Ames Laboratory, One-minute Measurement

- SPMD

Single Program Multiple Data

System Performance Evaluation Group

PerPreT variable for number of statements

- SUT

System under test

-  $t_{comm}$ Communication time

- t<sub>exec</sub>

Execution time

- *t*<sub>over</sub> Overhead time

- TPS

Transactions per second

## 1. Introduction

# 1.1. Basic Classification of Performance Analysis

The growing number of different parallel computer architectures demands methods for a comparison of these systems relative to performance issues. To increase reliability and performance of computing systems is an important motivation for the development of new processors and computer architectures.

Two basic techniques to achieve higher performance can be observed, either improvements in chip technology are made and/or architectural improvements, especially parallelism, are used. The chips are getting larger, the transistors on chip are getting smaller as are the connections on chip. Higher frequencies are used. Thus, the performance upgrades of the last decades were possible. It is difficult to predict, when the chip technology will reach its physical restraints that can no longer be overcome (speed of light for frequency, connections that are less than one atom wide). If the physical limits of chip technology are reached, parallelism is the only alternative to further upgrade performance. Parallelism is already used in all computing systems on levels ranging from register width to number of concurrently running processors.

Existing parallel systems can roughly be classified in two categories, namely, SIMD- (single instruction, multiple data) and MIMD-(multiple instruction, multiple data) architectures. As the classification indicates, the performance of SIMD-architectures is mainly based on data parallelism. Many processors or ALUs (arithmetic logical units) are executing the same instruction synchronously on different data. Such systems were very successful at the beginning of the development of parallel systems. Later they were replaced by more flexible and more powerful MIMDarchitectures. The methods presented in this book mainly describe approaches for the performance analysis of MIMD-systems.

Performance analysis of computing systems is carried out by:

2 Introduction

- computer architects

- computer vendors and buyers

- system software developers

- application developers.

The results of the performance analysis are used to:

- improve the architecture

- detect and eliminate bottlenecks

- compare systems.

The performance of a system is vitally important to the vendor and buyer. Looking at figures like MIPS (mega instructions per second), or MFLOPS (mega floating point operations per second), or TPS (transactions per second) in order to describe the performance of a system in a vendor's catalogue does not necessarily inform the potential buyer of the true performance. First of all, these numbers are always peak performances, meaning these numbers are true (if at all) only for a very limited selection of applications. They

are less useful if a user is interested in the performance of the target system for specific applications. This problem is well known from single processor architectures, however, it is more important and more complex for multiprocessor systems. The total performance of such a system is not only determined by the processor performance but also by the memory management strategy (in case of shared memory systems), network architecture, system throughput, communication, and synchronization management strategies.

The approaches for performance analysis of computer systems can be divided into three categories:

- performance measurement,

- performance modeling,

- and performance simulation.

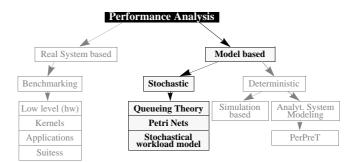

In [Lin98] a basic classification of these performance evaluation techniques is given (compare Fig. 1.1.).

#### **Performance Measurement**

The main goal for deterministic evaluation techniques based on performance measurement of real systems is to find performance bottlenecks and, if possible, to minimize them. Normally it is not possible to change the hardware of existing systems, but the results can be used to improve the design of successor systems. Another possibility is to add hardware to reduce system bottlenecks if the system is scalable. A tuning of the system software is also often possible.

The load used for the performance measurement can be a suite of real applications or a workload model can be used (compare Fig. 1.2.). The results of performance measurement techniques compared with performance modeling techniques are more dependable and accurate, since no losses of accuracy through model abstraction can occur.

## **Performance Modeling**

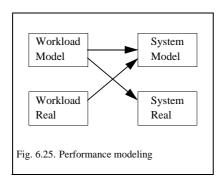

For performance modeling techniques, the system load or the system architecture, or both, are represented through a model (compare Fig. 1.3.).

Deterministic and stochastic models are easier and more efficient to analyze the performance of future systems than performance measurement, because hardware prototypes are expensive to realize. Any representation of reality through models is an abstraction of reality and, thus, suffers from a loss of accuracy. The more detailed and complex a model

is, the better the accuracy is likely to be. It is important to make reasonable assumptions regarding the structure and detail of the models. The art of modeling is to find a good trade-off between needed accuracy and degree of abstraction. Performance modeling using deterministic and stochastic models becomes very complex and difficult if the dynamic behavior of parallel applications on MIMD-systems has to be examined in detail.

## **Performance Simulation**

Performance simulation techniques use a system simulator to execute a model of the workload or the real workload (compare Fig. 1.4.). Performance simulation is well suited for complex architectures which are difficult to model (especially dynamic behavior). The problems in performance simulation are extremely long runtimes which allow only small workload models or small real workloads.

Introduction

# 1.2. Refined Classification of Performance Analysis

This text includes a survey of methods from two categories (performance measurement and performance modeling) and a short summary on performance simulation. An answer to the question which method should be used for which problem will be given. Possible problems are:

- purchase decision

- architectural improvements

- optimization of applications

#### **Purchase Decision**

One use of models is to help determine the computer with the best price/performance ratio for a user's needs. Two scenarios are possible: the best machine for a given amount of money has to be found, or the cheapest machine to fulfill given requirements has to be found.

## **Architectural Improvements**

A main goal of the system designer is to improve the architecture of the system. These improvements cannot always be realized in hardware because it is too expensive or too time consuming. Using performance analysis techniques (measurement, modeling, simulation) can help to dramatically reduce the cost and time in computer development.

## **Optimization of Applications**

In addition to buyers and system designers, application developers use performance analysis techniques. The main goal is, in this case, improvement of the user's applications. Parallel applications especially offer a high potential of optimization which is often not fully realized. Performance analysis allows the comparison of different versions of parallel

applications in terms of runtime and efficiency without the need to implement them on a real machine. Furthermore, analysis can save time and money compared to real implementations. This effect is especially important for multiprocessor systems, because the implementation and testing of different versions of an algorithm is much more complex than doing the same on a monoprocessor.

Additionally, since implementations are not always portable among different multiprocessor systems, a new workload program for every system is necessary. Only a few approaches for common parallel languages ([PICL90], [MPI95], [Lin85]) exist, but none of them is accepted as a standard language. The systems do not only differ in programming language but also in the programming model used which often is a reflection of the system architecture (message passing, shared memory). This is one of the reasons for the low acceptance of multiprocessor systems which often show a better performance/price ratio than comparable vector processor systems

A survey of existing and important performance analysis techniques is given in this text. Two new approaches for the performance evaluation of multiprocessor systems are presented, a benchmark generator and a modeling technique for massively parallel systems. The latter techniques is used for a complete performance evaluation and prediction tool which is presented in the last part of this toxt.

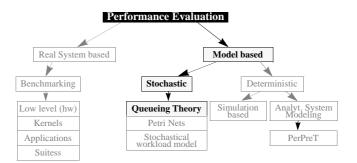

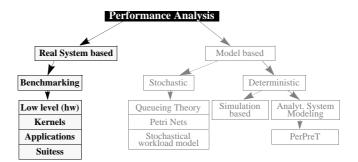

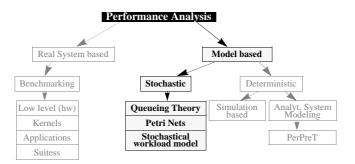

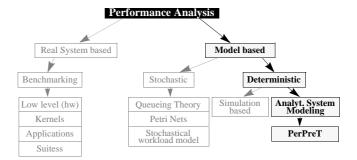

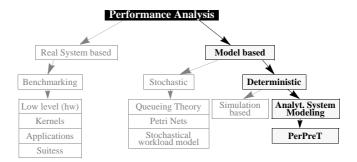

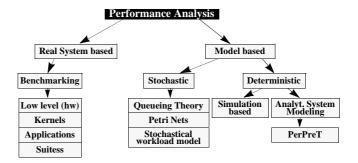

The basic classification of performance evaluation techniques (compare Fig. 1.1.) is now refined to be better be able to show the reader of this text the context of the described techniques. As shown in Fig. 1.5. performance evaluation can be carried out on real systems, on prototypes, or on models of real systems.

If a real system and its workload is available benchmarking is used to determine the performance. The prototype of a real system allows profiling techniques, low level test of the hardware and elapsed time benchmarking. If the real system is not built yet or not available, model based techniques have to be

applied. they are divided into stochastic methods using queueing theory, Petri Nets or analytical models. The deterministic approaches are either simulation based or the system and workload are described by analytical models.

Fig. 1.5. Refined classification of performance analysis techniques

6 Introduction

# 1.3. Organization of this Book

The first part of this book introduces and defines the basic notation in connection with performance analysis. The performance mea-

sures used and their meaning for computer architects are explained.

The next two sections describe the state of the art of performance measurement techniques based on deterministic evaluation for monoand multiprocessor systems. A new approach for multiprocessor performance evaluation, the LOOP Language, is presented. Especially for multiprocessors, performance modeling techniques seem to be important. The different approaches for stochastic performance

modeling are presented in the next part of the book. Stochastic modeling using Markov Chains or Petri Nets is discussed in section 5. A new approach for performance prediction using analytical parameterized models is presented in section 6. A case study shows the accuracy and usability of this approach. The last part of the book describes the resulting software tool of this performance evaluation

and prediction approach called PerPreT (Performance Prediction Tool).

The classification scheme shown in Fig. 1.6. is used throughout the rest of the book as an orientation help. It is displayed at the beginning of each chapter and the topics covered by the chapter are highlighted through bold boxes and names. Performance simulation is not subject of this book. However, some general information on this topic and some links to literature are given in section 3.3.

## 2. Basic Notation and Definitions

## 2.1. Notation

Computer scientists and researchers in performance analysis use many abbreviations and notations which are not always precise or sometimes used in different interpretations. Because of this disparity and for the better understanding, all relevant notation is defined and briefly explained in this section. If the meaning of a term is not unique it is explained how it is used in the context of this text.

## 2.1.1. General Terms in the Context of this Work

#### **Benchmark Program**

A benchmark program is a specific software with the goal to analyze the performance of a target system to be able to compare it with other systems. A benchmark program can be a real application or a synthetic program with the characteristics of a real application. Depending on the application, the benchmark program can stress single resources as memory access, arithmetic units, logical units, input/output devices or it can stress the system

as a whole. In order to use the benchmark program to compare various target systems it should be portable to a wide variety of machines.

#### **Benchmark Test**

A benchmark test is the execution of a benchmark program on a target system. To keep results comparable, some rules (e.g., compiler options, no manual optimizations, system

configuration) apply, or the system and benchmark properties are written down in a protocol. The results of a benchmark test are typically performance figures like MIPS (mega instructions per second), MFLOPS (mega floating point operations per second), TPS (transactions per second), or predefined performance characteristics like SPECints and SPECrates (compare section 3.1.3. and [SPEC95]).

#### Workload

The workload of a system consists of a set of operations which are executed on the system. Using different levels of abstraction, a workload can be an algorithm, a kernel of an application, a synthetic program, or a real application. The operations can be arithmetic operations, instructions, database operations, or other operations to stress specific parts of the system.

#### Kernel

A kernel is the computationally intensive part of an application. It often consists of a small number of code lines or of some loop cascades. For simplicity, kernels are extracted from complex applications and used as benchmark programs. As in synthetic workloads, operating system issues such as I/O are often neglected in kernels.

## Application

An application is a program to solve a problem on a computer. In contrast to kernels or synthetic programs, real problems are solved.

## **Parallel Application**

A parallel application is a program to solve a problem on a multiprocessor. The program includes programming constructs which allows the problem to be solved concurrently using more than one processor. Besides con-

structs for the concurrent execution it normally also provides constructs for the communication and synchronization of subtasks. The goal is to reduce the application's execution time when allocated an increasing number of processors.

#### Processor, Node

In this text, processor, node, processor node, processing element, and node processor are used synonymously in connection with multiprocessors. A node consists of a CPU (central processing unit) and a link to a main memory module. The CPU can be directly connected (exclusive access) to a main memory module or it can be connected via a interconnection network with the main memory module (multiple CPUs have access).

#### Monoprocessor

A monoprocessor is a computer that consists of one processor to execute programs. In the literature a monoprocessor system is also called single processor system or uniprocessor system. These terms are used synonymously throughout this text.

## Multiprocessor

A multiprocessor consists of several processors configured to execute programs concurrently. In contrast to a workstation cluster or computers loosely coupled via a LAN (large area network), the processors are tightly coupled, operate under the same operating system, and include a programming environment or language with programming constructs or routines for synchronization and communication. In the context of this book, the terms multiprocessor, parallel processing system, multicomputer, and MIMD system are equivalent.

Notation 1

#### **Massively Parallel System**

A multiprocessor is called massively parallel if it consists of more than 100 processors. This number is arbitrarily chosen to distinguish between parallel and massively parallel. It reflects today's systems. Systems consisting of up to several thousands of processors are commercially available.

#### **Performance Prediction**

The results of performance modeling or simulation allow performance predictions for a system. The predictions can be for workload models, for applications, or more general systems. For example, the peak performance of a computing system can be predicted. Examples for performance measures are execution time, speedup, and efficiency (for definition of performance measures, see section 2.2.2.).

#### Performance Evaluation / Analysis

The results of benchmark tests are used for the performance evaluation of a system. The performance of the system is measured in terms of operations per time unit. The operations can be basic instructions, arithmetic operations (floating point or integer), or transactions in case of data base systems. Methods for performance evaluation use measurement, modeling, and simulation. The terms performance evaluation and performance analysis are used synonymously in this book.

#### **Peak Performance**

The maximum performance of a system is called peak performance. There are two different ways to find the peak performance of a system:

- Perform several benchmark tests and use the results as the sustained peak performance for these tests.

- Calculate the peak performance using the architectural parameters. For example, the

peak performance can be found by taking the performance of the execution unit, multiply it by the number of execution units per processor and multiply it by the number of processors in case of a multiprocessor systems. The result is the theoretical peak performance, an unrealistic number often used by computer vendors.

Since the theoretical peak performance is calculated without a workload, performance losses by memory access, system software (compiler, operating system, etc.), and possibly synchronization and communication in case of multiprocessors, the theoretical peak performance is, in general, much higher than the sustained peak performance.

#### **Communication Bandwidth**

Parallel applications running concurrently on multiprocessors require mechanisms for communication and synchronization. The maximum amount of data that can be transferred during a time unit between a pair of processors is defined as communication bandwidth. The communication can be realized by links connecting processors in the case of distributed memory systems or by access to common data in the case of shared memory systems. The different multiprocessor architectures are explained in section 4.1. The peak communication bandwidth of a distributed memory multiprocessor is the sum of the concurrent link bandwidths. The peak communication bandwidth of a shared memory multiprocessor is determined by the bandwidth between processors and memory. As discussed for computational peak performance, the communication peak performance can be calculated using the architectural parameters (theoretical communication peak performance) or it can be determined by communication benchmarks (sustained communication peak performance).

## 2.1.2. Program Task Graphs

Performance analysis often use Program Task Graphs (PTGs) to formally describe workloads [Kat96]. A PTG is defined as a directed acyclic graph. The nodes represent tasks and the edges represent communication relations between the tasks. The edges and the nodes can have attributes to describe the timings of the tasks and communications.

In Fig. 2.1. a simple example for a PTG is given. The workload is divided into small units (subtasks). Each subtask is represented by a PTG node. The nodes can carry attributes to represent the weight of the subtask. Possible attributes are: number of instructions, time units, number of arithmetic operations, number of transactions when dealing with a data base, number of memory accesses, and others. The edges (arrows) between the subtasks show the data dependencies. In the case of multiprocessor workloads, data dependencies are solved by synchronization and communication between the

subtasks. Like the nodes, the edges can carry attributes with weight functions, such as timings for a message transfer, or synchronization timings, or message lengths. The description of a parallel (multiprocessor) workload as a PTG makes it easy to distribute the subtasks onto the processors.

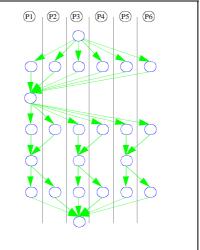

As an example, the PTG of Fig. 2.1. is mapped onto six processors in Fig. 2.2. The data dependencies (edges) represent the communications between the processors. A limitation of the PTG representation is that communication arrows have to be deterministic.

Fig. 2.2. Mapping of a parallel workload described by a PTG onto 6 processors

If the execution times of the subtasks and the timing of the communication are known, an optimization of the mapping of the PTG onto the processors can be carried out. The goal of the optimization is to minimize the total execution time [Kat96].

# 2.2. Performance Analysis Definitions

## **2.2.1.** Timing

#### **Execution Time**

The execution time of a program  $t_{exec}$  in the scope of this text is the time from the execution of the first program instruction until the last program instruction. Program loading times are not considered here. For parallel programs that are executed by one or more processors the same definition is used.

$$t_{exec} = T_{stop} - T_{start}$$

(Eq.2.1)

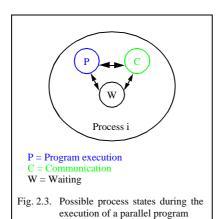

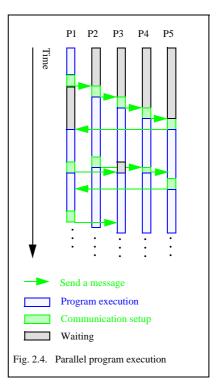

The execution time of a parallel program normally consists of three portions, namely program execution time (instructions and operations), communication time, and waiting time.

The portions result from the times the processes are in the different states "Program ex-

ecution (P)", "Communication (C)", or "Waiting (W)" (compare Fig. 2.3. and Fig. 2.4.)

## **Communication Time**

The communication time of a parallel program  $t_{comm}$  is the sum of the times for the communication between the processors:

$$t_{comm} = \sum_{i} t_{msg}^{i}$$

(Eq.2.2)

with i = 1, 2, ..., number of messages.

The time for one communication between a pair of processors in a message passing system  $t_{msg}$  is divided into three portions: setup time for the sending of a message  $t_{ss}$  transfer time  $t_t$  and receive time  $t_{rec}$ .

$$t_{msg} = t_{ss} + t_t + t_{rec}$$

(Eq.2.3)

#### **Synchronization Time**

The synchronization time  $t_{sync}$  is the time spend for synchronization operations. A typical synchronization operation is a global barrier, i.e. all concurrently running processes wait at a global synchronization point specified in the parallel program until the last process arrives at this point (called barrier). This arrival releases all processes and they may continue.

#### **Waiting Time**

The difference between synchronization time  $t_{sync}$  and waiting time  $t_{wait}$  is that the time  $t_{wait}$  is caused by waiting for communication, i.e. one process would like to receive a message that is not available yet. Since the operation  $receive\ message$  is normally blocking, the process has to wait until the message has arrived.

#### **Overhead Time**

The sum of times used for synchronization  $t_{sync}$  added to the sum of waiting times  $t_{wait}$  results in a time called overhead time  $t_{over}$ :

$$t_{over} = \sum_{k} t_{sync}^{k} + \sum_{m} t_{wait}^{m}$$

(Eq.2.4)

with k = 1,2,..., number of synchronizations and with m = 1,2,..., number of waits.

#### **Computation Time**

The computation time  $t_{comp}$  is the sum of all times during which the processes are in the program execution state.

#### **Total Execution Time**

The total execution time  $t_{total}$  of a parallel program is defined as  $t_{exec}$  in the beginning of this section. Using its portions, the total execution time can be rewritten as the sum of computation, communication, and overhead time, divided by the number of processors:

$$t_{total} = \frac{t_{comp} + t_{comm} + t_{over}}{P}$$

(Eq.2.5)

with P = number of processors.

Since the portions  $t_{comm}$ ,  $t_{comp}$ , and  $t_{over}$  are always sums of times for all processors, the division by P (number of processors) has to be carried out. Minimizing the total execution time of a parallel program is achieved by minimizing all portions of the sum. Communication, synchronization, and overhead times expressed by  $t_{comm}$  and  $t_{over}$  can be reduced by intelligent mapping of subtasks onto the processors. Computation time can be reduced by more efficient algorithms. Unfortunately, more efficient algorithms often lead to a more demanding communication structure in the parallel program, thus creating a trade-off between minimizing t<sub>comm</sub> and  $t_{comp}$ . This trade-off is also system dependent leading to different implementations for different systems. One goal of performance modeling techniques is to help the user to minimize the total execution time of a parallel program.

## 2.2.2. Performance Measures

The basic definition of performance is work divided by time which is also valid for computers.

## Throughput

Throughput matches the basic definition of performance best. This performance measure describes in general the number of requests that are completed per time unit. Request is another word for workload, a request can be a transaction in terms of data base systems, it can be a job in terms of batch systems, it can simply be a user request in terms of interactive systems, or it can be the execution of an instruction or operation. The resulting performance measures are MIPS (millions of instructions per second), MFLOPS (millions of floating point operations per second), and TPS (transactions per second), or simply jobs per second. Other performance measures depending on the definition of work units are possible.

Performance measures are system and application specific. To determine the performance of an application for a system, the total execution time  $t_{exec}$  has to be calculated or

measured. The work (characterized by its units) divided by  $t_{exec}$  (and if needed by  $10^6$  for "Mega") results in the corresponding performance measure.

Unfortunately, marketing reasons have led to a widespread misuse of performance measures. A hardware provider is interested in offering a "high" performance system. Often, performance measures are calculated using the hardware description of the system without taking the compiler and operating systems into account. These theoretical "peak" performances are normally much higher than the performances for real applications.

#### Utilization

Utilization is a measure of how busy the resource system is when used by a specific workload. In terms of parallel systems, the utilization is also called efficiency (as defined later in this section).

## Response Time

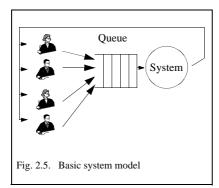

As outlined in Fig. 2.5., some users can share an interactive system, wait for the results, and, based on the results, initiate new jobs to the queue. The time a job spends in the system (from entering the queue until completion) is the job's response time.

#### **Queue Length**

The queue length directly relates to the time a job must wait until it is executed by the system. The queue length is the average number of jobs in the queue or receiving service.

#### 2.2.3. Relative Performance Measures

Since absolute performance measures such as MIPS, MFLOPS, or TPS for a computer architecture are theoretically calculated numbers that are not reached for real applications, it is often better to work with relative performance measures. By which factor the execution of an application can be accelerated using a multiprocessor is a very common question. System designers think about by which factor a new architecture is faster than its predecessor. These and similar questions can be answered using relative performance measures such as speedup, scaleup, efficiency, and reference numbers such as performance ratios.

## Speedup

The goal of the application parallelization is the minimization of the total execution time  $t_{exec}$  through the concurrent execution of the application on several processors. Gene Amdahl [Amd67] was one of the first who considered the problem of the maximum possible speedup. The definition of speedup is the relation of total execution time  $t_{e,I}$  on one processor to total execution time  $t_{e,P}$  on P processors. In Amdahl's approach, an application is divided into a sequential and a parallel fraction. The execution time of the sequential fraction is constant no matter how many processors are involved. The execution time of the parallel fraction decreases proportionally to the number of allocated processors.

Amdahl's law describes the speedup behavior of parallel applications. It is derived from the following approach:

The execution time of an application  $t_{e,I}$  is:

$$t_{e, 1} = t_{es} + t_{ep, 1}$$

(Eq.2.6)

where  $t_{ex}$  is the execution time for the sequential fraction and  $t_{ep,I}$  is the execution time of the parallel fraction on one processor. The sequential fraction seq and the parallel fraction par are defined as:

$$seq = \frac{t_{es}}{t_{ep, 1} + t_{es}}$$

(Eq.2.7)

$$par = \frac{t_{ep, 1}}{t_{ep, 1} + t_{es}}$$

(Eq.2.8)

and thus,

$$par = 1 - seq$$

(Eq.2.9)

The total execution time  $t_{e,P}$  for P processors is:

$$t_{e, P} = t_{es} + \frac{t_{ep, 1}}{P}$$

(Eq.2.10)

Using *P* processors results in the speedup factor  $S_p$ :

$$S_P = \frac{t_{e, 1}}{t_{e, p}} = \frac{t_{es} + t_{ep, 1}}{t_{es} + \frac{t_{ep, 1}}{P}}$$

(Eq.2.11)

Using (Eq.2.7), the expression from (Eq.2.11) can be transformed to:

$$S_{P} = \frac{1}{\frac{t_{es}}{t_{es} + t_{ep, 1}} + \frac{t_{ep, 1}}{t_{es} + t_{ep, 1}} \cdot \frac{1}{P}}$$

which is equivalent to:

$$S_P = \frac{1}{seq + par \cdot \frac{1}{P}}$$

(Eq.2.12)

This last equation is called *Amdahl's law*. It shows the heavy impact of the sequential fraction seq of a parallel program that is executed on P processors. If seq is only one percent (seq = 0.01) the maximum speedup  $S_P$  is less than 100 (even for an unlimited number of processors P).

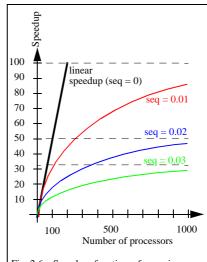

Since seq and par are constant, the  $S_p$  function approaches 1/seq as the number of processors increases. Fig. 2.6. shows speedup functions for different values of seq. For seq=0 (and, thus, par=1), the ideal speedup function  $S_p = P$  is derived from (Eq.2.11):

$$S_P = \frac{t_{e,1}}{t_{e,p}} = \frac{1}{0 + \frac{1}{P}} = P$$

(Eq.2.13)

Fig. 2.6. also shows speedup functions for seq=0.01, seq=0.02 and seq=0.03. For example, 1000 processors result in a speedup of less than 33 if the sequential fraction of a parallel application seq is 3 percent.

One of the consequences of Amdahl's law is that there are few applications that offer enough parallelism (i.e., *seq* is very small) to result in close to linear speedup functions on massively parallel systems.

This is also demonstrated by the efficiency of parallel applications.

Fig. 2.6. Speedup functions for various seq using Amdahl's law.

## Efficiency

The efficiency of a parallel application running on *P* processors is defined as:

$$\varepsilon = \frac{S_P}{P}$$

(Eq.2.14)

Speedup is defined in (Eq.2.12). If par is replaced in this equation by (1-seq) using (Eq.2.9),  $\epsilon$  can be written as:

$$\varepsilon = \frac{1}{1 + seq \cdot (P - 1)}$$

Examples of efficiency functions over *seq* for various numbers of processors *P* are shown in Fig. 2.7. Considering the steep descent for a sequential fraction *seq* of 10% even for small numbers of processors, it becomes clear that

reasonable efficiency of parallel applications running on massively parallel systems is only possible for very small values of seq, i.e., seq << 0.01.

Fig. 2.7. Efficiency functions for various numbers of processors P

#### Scaleup

One reaction to Amdahl's law is the assumption that only few applications exist that offer enough parallelism for efficient implementations on multiprocessors with large numbers of processors. A resulting question is whether it is worth investing much money and effort in building these machines. Despite that pessimistic outlook, several multiprocessors with up to thousands of processors have been built (nCUBE Hypercube, Connection Machine, INTEL Paragon, CRAY T3D, compare section 6.1.3.) and many applications with reasonable efficiency have been implemented on these machines.

Gustafson explains this seeming contradiction to Amdahl's law in his article "Reevaluating Amdahl's Law" [Gus88]. The derivation of Amdahl's law (Eq.2.6) to (Eq.2.13) is

mathematically correct. The only problems are the pessimistic assumptions which are not necessarily true in real life. Amdahl assumes that the sequential fraction seq is constant and he does not examine the behavior of the sequential fraction for different problem sizes. These assumptions are different in Gustafson's approach. Gustafson points out that the sequential fraction does not necessarily grow linearly with the problem size. For many parallel applications seq grows slower or is even constant. This leads to the assumption observed in parallel applications that the total execution time of a parallel program remains constant for larger problem sizes if processors are added to execute it.

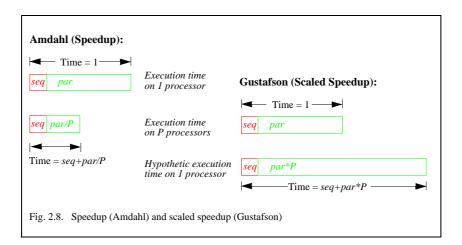

Fig. 2.8. shows the difference in the approaches of Amdahl and Gustafson. In the latter approach, the total execution time on a multiprocessor is the sum of the execution time for the sequential fraction *seq* and the execution time for the parallel fraction *par*. If only one processor is used to execute the program, the runtime of the parallel fraction *par* is multiplied by the number of processors *P*.

Gustafson defines the execution of a program on one processor as:

$$t_P = t_{es} + t_{ep} \cdot P \tag{Eq.2.15}$$

Thus, the execution time on P processors is:

$$t_1 = t_{es} + t_{ep}$$

(Eq.2.16)

and the resulting scaled speedup is:

$$SS_P = \frac{t_1}{t_p} = \frac{t_{es} + \frac{t_{ep}}{P}}{t_{es} + t_{ep}}$$

(Eq.2.17)

Using (Eq.2.7):

$$SS_P = \frac{seq + par \cdot P}{seq + par}$$

(Eq.2.18)

Using (Eq.2.9):

$$SS_P = P + (1 - P) \cdot seq$$

(Eq.2.19)

In contradiction to Amdahl, the scaled speedup function is linear. For small sequential fractions *seq*, the function is close to the ideal speedup curve. Gustafson's intention is not to disprove Amdahl's law but to show that there are real applications that offer enough parallelism for large problem sizes to run efficiently on massively parallel systems. It also shows that it does not make good sense to use large multiprocessor systems for the solution of small problems.

## Reference Measures

In the late 1980's several major hardware providers (IBM, SUN, HP, SIEMENS, and others) founded an institution with the goal of devising a fair performance evaluation of computer systems. To reach its goal they collected real applications and used them for the performance evaluation. The consortium was called SPEC (System Performance Evaluation Cooperative). A list with the 10 applications of the release 1 of the SPEC consortium is shown in Tab. 2.1.

These applications are execution time intensive and the influence of operating system calls during execution is negligible. The cal-

culation of the so called SPECmark for a target system takes four steps:

- Determination of total execution time for every program i on target system z results in t<sub>iz</sub>.

- Determination of total execution time for every program i on reference system r (VAX 11/780) results in t<sub>ir</sub>.

- The relation of  $\mathbf{t}_{ir}$  to  $\mathbf{t}_{iz}$  is called SPECratio  $\mathbf{R}_{izr}$ :

$$R_{izr} = \frac{t_{ir}}{t_{iz}}$$

- Calculation of geometric mean  $\overline{R}_{g\ zr}$  for the 10 test programs.  $\overline{R}_{g\ zr}$  is called SPECmark.

Speedup and scaleup are important relative measures for multiprocessor system whereas

SPECmarks are mainly used to compare monoprocessor systems. A more detailed description of the SPEC Benchmarks can be found in section 3.1.

| Abbreviation | Workload                                  | Program | Data  |

|--------------|-------------------------------------------|---------|-------|

| gcc          | GNU C-Compiler                            | С       | int   |

| espresso     | PLA-Simulator                             | С       | int   |

| spice2g6     | Analog circuit simulation                 | Fortran | float |

| doduc        | Monte Carlo Simulation                    | Fortran | float |

| nasa7        | Collection of numerical "kernels"         | Fortran | float |

| li           | LISP Interpreter                          | С       | int   |

| eqntott      | Minimization of boolean functions         | С       | int   |

| matrix300    | Several matrix multiplications            | Fortran | float |

| fpppp        | Solution of the Maxwell Equations         | Fortran | float |

| tomcatv      | Network computations, strongly vectorized | Fortran | float |

Tab. 2.1. SPEC CPU benchmarks (Release 1)

## 2.2.4. System Under Test

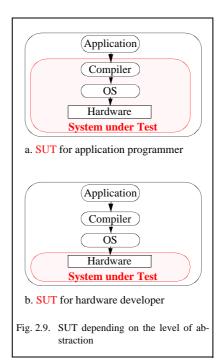

There are several approaches to the evaluation of systems, depending on the chosen level of abstraction. Although there is a continuum of possible views, two examples of different abstraction levels are illustrated in Fig. 2.9.

For the programmer of a high level application, the system under test (SUT) includes several components such as the compiler, the operating system, and the underlying hardware. In a multiprocessor environment, the interconnection network is also part of the SUT. The programmer might be interested in several performance features including:

- response time,

- elapsed time,

- resource utilization,

- communication patterns,

- concurrency profile, and

- space-time-diagram.

A different view of the same computer system is shown in Fig. 2.9.b. A hardware developer is normally less interested in the performance of the compiler or the operating system. Thus, the benchmarks of most use are specifically designed for the evaluation of certain hardware components of interest. The features of most interest to the hardware developer include:

- native MIPS,

- cache hit rate,

- bus utilization, and

- memory access times.

The system under test considered throughout this text is the one of the application programmer, Fig. 2.9.a. The compiler, the operating system, and the underlying hardware will be regarded as a black box. The instrumentation

results in data for the single node performance, the communication behavior, and the overall performance. Looking at the amount and speed of communication at the nodes, potential and existing bottlenecks in the interconnection network are identified.

The methods for performance evaluation of monoprocessor systems and the methods for performance evaluation of multiprocessor systems mainly differ in the way to determine or define the workload for the performance tests and in the way the tests are realized on the target system. Three different approaches are used:

- The target system is a real system and the workload is executed on the system. This method is called benchmarking.

- The properties of the target system are captured by a simulator. The SUT is defined as in Fig. 2.9., where the hardware is replaced by a simulator in this figure. Since modern microprocessors are very complex, the simulator runs are very time consuming. Depending on the complexity of the hardware and the simulators, slowdowns with a factor from 100 to 10<sup>6</sup> or more are possible. This means that to simulate one second of

- execution time, the simulator might need more than one week.

- This slowdown leads to a third approach where the simulator is replaced by a model for the hardware and workload. The accuracy, and thus, complexity of the hardware model depends on the desired accuracy of the results.

For all three approaches the workload can be either real applications or models with the properties of the desired applications.

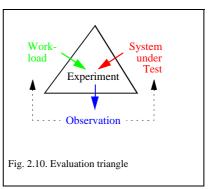

#### 2.2.5. Evaluation Triangle

Generally speaking, any kind of evaluation can be described by the evaluation triangle as shown in Fig. 2.10. An evaluation requires an experiment which runs a *workload* on a specific platform within a given environment (SUT). The experiment is subject to an *observation* producing results which possibly lead to a redesign of the workload and/or the target system. In the next two sections of this text, the experiment is benchmarking for monoprocessors and multiprocessors. The workloads are synthetic (low level, kernels) and real (applications). The SUT is a real machine.

# 3. Performance Analysis of Monoprocessors

The first part of this section describes the generation and definition of workloads for performance tests and some examples for benchmarking with synthetic workloads and applications. The second part of this section presents an important approach for performance modeling of monoprocessor systems, namely, queueing networks. This general stochastic modeling technique, its graphical system and workload representation, the derivation of the steady-state diagram, and the solution of the linear system of equations for birth-death models is explained.

Benchmarking consists of two steps. First a workload is selected. The user has the choice of predefined standard workloads as present-