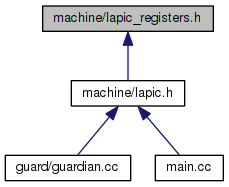

Strukturen und Makros zum Zugriff auf den Local APIC. Mehr ...

#include "types.h"

Klassen | |

| struct | LAPICID_P |

| Local APICID Register für P6 und Pentium. Mehr ... | |

| struct | LAPICID_P4 |

| Local APIC ID Register für Pentium IV und spätere. Mehr ... | |

| struct | LAPICVER |

| Local APIC Version Register. Mehr ... | |

| struct | ICR_L |

| Interrupt Command Register Low. Mehr ... | |

| struct | LAPICTimer_Control |

| LAPIC-Timer Control Register. Mehr ... | |

| struct | ICR_H |

| Interrupt Command Register High. Mehr ... | |

| struct | LDR |

| Logical Destination Register. Mehr ... | |

| struct | DFR |

| Destination Format Register. Mehr ... | |

| struct | TPR |

| Task Priority Register. Mehr ... | |

| struct | SVR |

| Spurious Interrupt Vector Register. Mehr ... | |

Makrodefinitionen | |

| #define | DESTINATION_SHORTHAND_NO 0x0 |

| Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs. Mehr ... | |

| #define | DESTINATION_SHORTHAND_SELF 0x1 |

| Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs. Mehr ... | |

| #define | DESTINATION_SHORTHAND_ALLINCSELF 0x2 |

| Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs. Mehr ... | |

| #define | DESTINATION_SHORTHAND_ALLEXCSELF 0x3 |

| Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs. Mehr ... | |

| #define | TRIGGER_MODE_EDGE 0x0 |

| Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs. Mehr ... | |

| #define | TRIGGER_MODE_LEVEL 0x1 |

| Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs. Mehr ... | |

| #define | LEVEL_DEASSERT 0x0 |

| Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs. Mehr ... | |

| #define | LEVEL_ASSERT 0x1 |

| Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs. Mehr ... | |

| #define | DELIVERY_STATUS_IDLE 0x0 |

| Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs. Mehr ... | |

| #define | DELIVERY_STATUS_SEND_PENDING 0x1 |

| Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs. Mehr ... | |

| #define | DESTINATION_MODE_PHYSICAL 0x0 |

| Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs. Mehr ... | |

| #define | DESTINATION_MODE_LOGICAL 0x1 |

| Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs. Mehr ... | |

| #define | DELIVERY_MODE_FIXED 0x0 |

| Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs. Mehr ... | |

| #define | DELIVERY_MODE_LOWESTPRI 0x1 |

| Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs. Mehr ... | |

| #define | DELIVERY_MODE_SMI 0x2 |

| Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs. Mehr ... | |

| #define | DELIVERY_MODE_NMI 0x4 |

| Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs. Mehr ... | |

| #define | DELIVERY_MODE_INIT 0x5 |

| Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs. Mehr ... | |

| #define | DELIVERY_MODE_STARTUP 0x6 |

| Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs. Mehr ... | |

| #define | DESTINATION_MODEL_CLUSTER 0x0 |

| Einstellungsmöglichkeiten und Modi für das DFR Register. Mehr ... | |

| #define | DESTINATION_MODEL_FLAT 0xf |

| Einstellungsmöglichkeiten und Modi für das DFR Register. Mehr ... | |

| #define | FOCUS_CPU_ENABLED 0x0 |

| Einstellungsmöglichkeiten und Modi für das SVR Register. Mehr ... | |

| #define | FOCUS_CPU_DISABLED 0x1 |

| Einstellungsmöglichkeiten und Modi für das SVR Register. Mehr ... | |

| #define | LAPIC_DISABLED 0x0 |

| Einstellungsmöglichkeiten und Modi für das SVR Register. Mehr ... | |

| #define | LAPIC_ENABLED 0x1 |

| Einstellungsmöglichkeiten und Modi für das SVR Register. Mehr ... | |

Ausführliche Beschreibung

Strukturen und Makros zum Zugriff auf den Local APIC.

Makro-Dokumentation

◆ DELIVERY_MODE_FIXED

| #define DELIVERY_MODE_FIXED 0x0 |

Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs.

siehe: System Programming Guide 3A, p. 9-39 bzw. IO-APIC manual, p. 11-13

◆ DELIVERY_MODE_INIT

| #define DELIVERY_MODE_INIT 0x5 |

Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs.

siehe: System Programming Guide 3A, p. 9-39 bzw. IO-APIC manual, p. 11-13

◆ DELIVERY_MODE_LOWESTPRI

| #define DELIVERY_MODE_LOWESTPRI 0x1 |

Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs.

siehe: System Programming Guide 3A, p. 9-39 bzw. IO-APIC manual, p. 11-13

◆ DELIVERY_MODE_NMI

| #define DELIVERY_MODE_NMI 0x4 |

Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs.

siehe: System Programming Guide 3A, p. 9-39 bzw. IO-APIC manual, p. 11-13

◆ DELIVERY_MODE_SMI

| #define DELIVERY_MODE_SMI 0x2 |

Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs.

siehe: System Programming Guide 3A, p. 9-39 bzw. IO-APIC manual, p. 11-13

◆ DELIVERY_MODE_STARTUP

| #define DELIVERY_MODE_STARTUP 0x6 |

Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs.

siehe: System Programming Guide 3A, p. 9-39 bzw. IO-APIC manual, p. 11-13

◆ DELIVERY_STATUS_IDLE

| #define DELIVERY_STATUS_IDLE 0x0 |

Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs.

siehe: System Programming Guide 3A, p. 9-39 bzw. IO-APIC manual, p. 11-13

◆ DELIVERY_STATUS_SEND_PENDING

| #define DELIVERY_STATUS_SEND_PENDING 0x1 |

Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs.

siehe: System Programming Guide 3A, p. 9-39 bzw. IO-APIC manual, p. 11-13

◆ DESTINATION_MODE_LOGICAL

| #define DESTINATION_MODE_LOGICAL 0x1 |

Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs.

siehe: System Programming Guide 3A, p. 9-39 bzw. IO-APIC manual, p. 11-13

◆ DESTINATION_MODE_PHYSICAL

| #define DESTINATION_MODE_PHYSICAL 0x0 |

Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs.

siehe: System Programming Guide 3A, p. 9-39 bzw. IO-APIC manual, p. 11-13

◆ DESTINATION_MODEL_CLUSTER

| #define DESTINATION_MODEL_CLUSTER 0x0 |

Einstellungsmöglichkeiten und Modi für das DFR Register.

System Programming Guide 3A, p. 9-48

◆ DESTINATION_MODEL_FLAT

| #define DESTINATION_MODEL_FLAT 0xf |

Einstellungsmöglichkeiten und Modi für das DFR Register.

System Programming Guide 3A, p. 9-48

◆ DESTINATION_SHORTHAND_ALLEXCSELF

| #define DESTINATION_SHORTHAND_ALLEXCSELF 0x3 |

Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs.

siehe: System Programming Guide 3A, p. 9-39 bzw. IO-APIC manual, p. 11-13

◆ DESTINATION_SHORTHAND_ALLINCSELF

| #define DESTINATION_SHORTHAND_ALLINCSELF 0x2 |

Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs.

siehe: System Programming Guide 3A, p. 9-39 bzw. IO-APIC manual, p. 11-13

◆ DESTINATION_SHORTHAND_NO

| #define DESTINATION_SHORTHAND_NO 0x0 |

Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs.

siehe: System Programming Guide 3A, p. 9-39 bzw. IO-APIC manual, p. 11-13

◆ DESTINATION_SHORTHAND_SELF

| #define DESTINATION_SHORTHAND_SELF 0x1 |

Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs.

siehe: System Programming Guide 3A, p. 9-39 bzw. IO-APIC manual, p. 11-13

◆ FOCUS_CPU_DISABLED

| #define FOCUS_CPU_DISABLED 0x1 |

Einstellungsmöglichkeiten und Modi für das SVR Register.

System Programming Guide 3A, p. 9-64

◆ FOCUS_CPU_ENABLED

| #define FOCUS_CPU_ENABLED 0x0 |

Einstellungsmöglichkeiten und Modi für das SVR Register.

System Programming Guide 3A, p. 9-64

◆ LAPIC_DISABLED

| #define LAPIC_DISABLED 0x0 |

Einstellungsmöglichkeiten und Modi für das SVR Register.

System Programming Guide 3A, p. 9-64

◆ LAPIC_ENABLED

| #define LAPIC_ENABLED 0x1 |

Einstellungsmöglichkeiten und Modi für das SVR Register.

System Programming Guide 3A, p. 9-64

◆ LEVEL_ASSERT

| #define LEVEL_ASSERT 0x1 |

Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs.

siehe: System Programming Guide 3A, p. 9-39 bzw. IO-APIC manual, p. 11-13

◆ LEVEL_DEASSERT

| #define LEVEL_DEASSERT 0x0 |

Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs.

siehe: System Programming Guide 3A, p. 9-39 bzw. IO-APIC manual, p. 11-13

◆ TRIGGER_MODE_EDGE

| #define TRIGGER_MODE_EDGE 0x0 |

Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs.

siehe: System Programming Guide 3A, p. 9-39 bzw. IO-APIC manual, p. 11-13

◆ TRIGGER_MODE_LEVEL

| #define TRIGGER_MODE_LEVEL 0x1 |

Einstellungsmöglichkeiten und Modi für die ICR_H und ICR_L Register bzw. für die IOREDTBL_H und IOREDTBL_L Register aus der Redirection-Tabelle des IO-APICs.

siehe: System Programming Guide 3A, p. 9-39 bzw. IO-APIC manual, p. 11-13